# PIC24FV32KA304 データシート

XLP テクノロジを採用した 20/28/44/48 ピン、汎用、 16 ビット フラッシュ マイクロコントローラ

#### マイクロチップ社製デバイスのコード保護機能に関して次の点にご注意ください。

- マイクロチップ社製品は、該当するマイクロチップ社データシートに記載の仕様を満たしています。

- マイクロチップ社では、通常の条件ならびに仕様に従って使用した場合、マイクロチップ社製品のセキュリティレベルは、現在市場に流通している同種製品の中でも最も高度であると考えています。

- しかし、コード保護機能を解除するための不正かつ違法な方法が存在する事もまた事実です。弊社の理解ではこうした手法は、マイクロチップ社データシートにある動作仕様書以外の方法でマイクロチップ社製品を使用する事になります。このような行為は知的所有権の侵害に該当する可能性が非常に高いと言えます。

- マイクロチップ社は、コードの保全性に懸念を抱くお客様と連携し、対応策に取り組んでいきます。

- マイクロチップ社を含む全ての半導体メーカーで、自社のコードのセキュリティを完全に保証できる企業はありません。コード保護機能とは、マイクロチップ社が製品を「解読不能」として保証するものではありません。

コード保護機能は常に進歩しています。マイクロチップ社では、常に製品のコード保護機能の改善に取り組んでいます。マイクロチップ社のコード保護機能の侵害は、デジタル ミレニアム著作権法に違反します。そのような行為によってソフトウェアまたはその他の著作物に不正なアクセスを受けた場合は、デジタル ミレニアム著作権法の定めるところにより損害賠償訴訟を起こす権利があります。

本書に記載されているデバイス アプリケーション等に関す る情報は、ユーザの便宜のためにのみ提供されているもので あり、更新によって無効とされる事があります。お客様のア プリケーションが仕様を満たす事を保証する責任は、お客様 にあります。マイクロチップ社は、明示的、暗黙的、書面、 口頭、法定のいずれであるかを問わず、本書に記載されてい る情報に関して、状態、品質、性能、品性、特定目的への適 合性をはじめとする、いかなる類の表明も保証も行いません。 マイクロチップ社は、本書の情報およびその使用に起因する 一切の責任を否認します。マイクロチップ社の明示的な書面 による承認なしに、生命維持装置あるいは生命安全用途にマ イクロチップ社の製品を使用する事は全て購入者のリスクと し、また購入者はこれによって発生したあらゆる損害、クレー ム、訴訟、費用に関して、マイクロチップ社は擁護され、免 責され、損害うけない事に同意するものとします。暗黙的あ るいは明示的を問わず、マイクロチップ社が知的財産権を保 有しているライセンスは一切譲渡されません。

### 商標

マイクロチップ社の名称と Microchip ロゴ、dsPIC、KEELOQ、KEELOQ ロゴ、MPLAB、PIC、PICmicro、PICSTART、rfPIC、UNI/O は、米国およびその他の国におけるマイクロチップ・テクノロジー社の登録商標です。

FilterLab、Hampshire、HI-TECH C、Linear Active Thermistor、MXDEV、MXLAB、SEEVAL、Embedded Control Solutions Company は、米国におけるマイクロチップ・テクノロジー社の登録商標です。

Analog-for-the-Digital Age,Application Maestro、chipKIT、chipKIT logo、CodeGuard、dsPICDEM、dsPICDEM.net、dsPICworks、dsSPEAK、ECAN、ECONOMONITOR、FanSense、HI-TIDE、In-Circuit Serial Programming、ICSP、Mindi、MiWi、MPASM、MPLAB Certifiedr ロゴ、MPLIB、MPLINK、mTouch、Omniscient Code Generation、PICC、PICC-18、PICDEM、PICDEM.net、PICkit、PICtail、REAL ICE、rfLAB、Select Mode、Total Endurance、TSHARC、UniWinDriver、WiperLock、ZENA は、米国およびその他の国におけるマイクロチップ・テクノロジー社の登録商標です。SQTP は、米国におけるマイクロチップ・テクノロジー社のサービスマークです。

その他、本書に記載されている商標は各社に帰属します。

© 2011, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-61341-032-5

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2009

マイクロチップ社では、Chandler および Tempe (アリゾナ州)、Gresham (オレゴン州) の本部、設計部およびウェハー製造工場そしてカリフォルニア州とイドのデザインセンターが ISO/TS-16949:2009 認証を取得しています。マイクロチップ社の品質システム プロセスおよび手順は、PIC® MCU および dsPIC® DSC、KEELoo® コードホッピング デバイス、シリアル EEPROM、マイクロペリフェラル、不揮発性メモリ、アナログ製品に採用されています。 さらに、開発システムの設計と製造に関するマイクロチップ社の品質システムは ISO 9001:2000 認証を取得しています。

### 20/28/44/48 ピン汎用 16 ビットフラッシュ XLP テクノロジ採用マイクロコントローラ

### 雷源管理モード:

- 動作モード CPU/ フラッシュ /SRAM/ 周辺モジュールは ON

- Doze モード CPU クロックが周辺モジュール用クロックよりも低速で動作

- アイドルモード CPU は OFF、フラッシュ/SRAM/ 周辺モジュールは ON

- スリープモード CPU/ フラッシュ/ 周辺モジュール は OFF、SRAM は ON

- ディープスリープ モード CPU/ フラッシュ /SRAM と大部分の周辺モジュールは OFF; 複数の自律的復帰 要因

- 低消費電力モード:

- 動作モード時の電流: 8 μA (Typical) まで低減

- アイドルモード時の電流: 2.2 μA (Typical) まで低減

- ディープスリープ モード時の電流:20 nA (Typical) まで低減

- リアルタイム クロック / カレンダ電流: 700 nA まで低減 (32 kHz/1.8 V 時 )

- ウォッチドッグ タイマ電流: 500 nA (1.8 V時、typical)

### 高性能 CPU:

- 改良型ハーバード アーキテクチャ

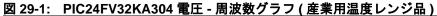

- 最大 16 MIPS の動作 (32 MHz 時)

- 8 MHz 内部オシレータに 4x PLL オプションと各種分 周オプションを併用可能

- 17 ビットx17 ビット シングルサイクル ハードウェア 乗算器

- 32 ビット/16 ビットのハードウェア除算器; 16 ビット x 16 ビットのワーキング レジスタアレイ

- Cコンパイラ向けに最適化された命令セットアーキテクチャ

### 周辺モジュールの機能:

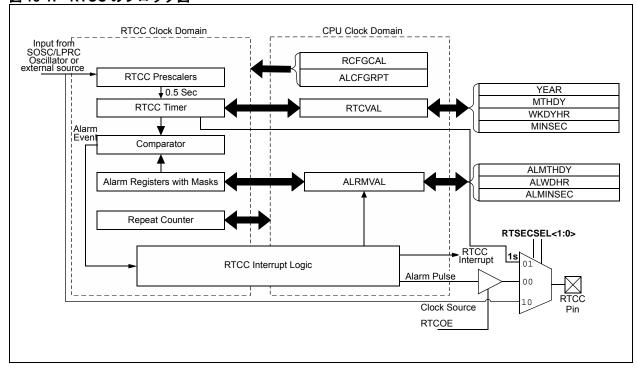

- ハードウェア リアルタイム クロック/カレンダ(RTCC)

- クロック、カレンダ、アラーム機能を提供

- ディープスリープモード中も動作可能

- 50/60 Hz 電源ライン入力をクロック源として使用 可能

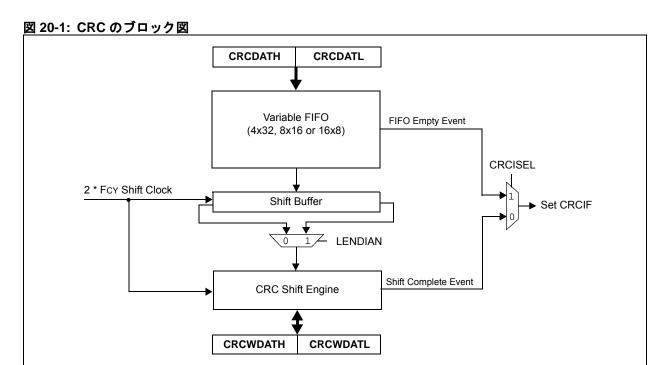

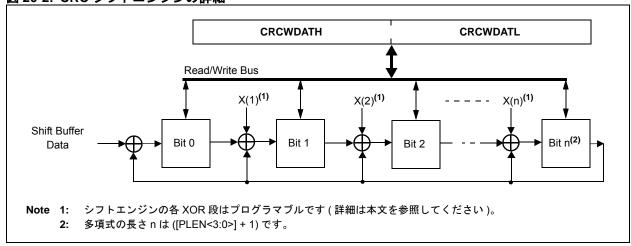

- 32 ビット プログラマブル巡回冗長検査 (CRC)

- ・ 複数のシリアル通信モジュール

- 2x3線/4線式SPIモジュール

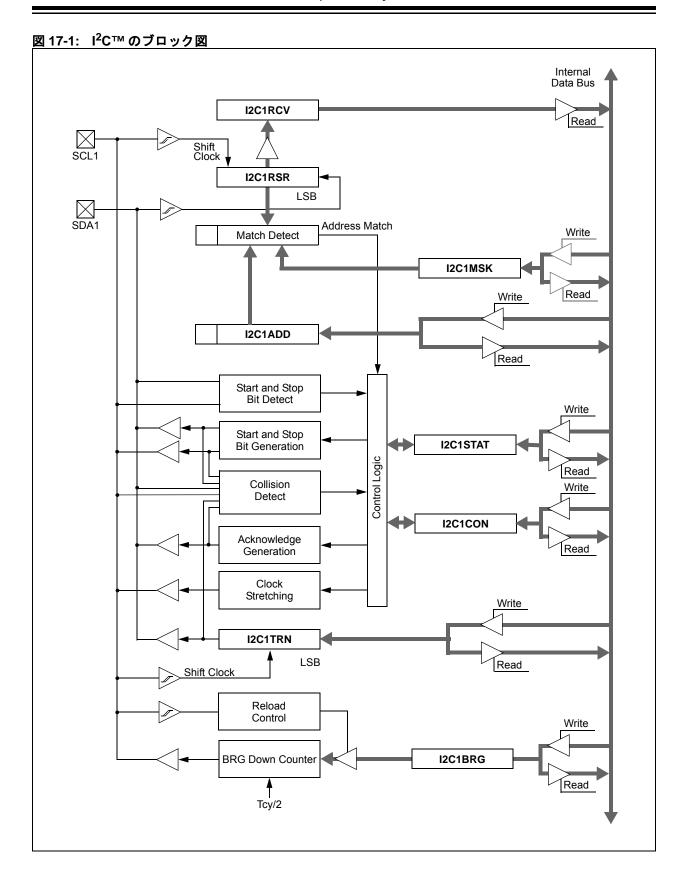

- 2 x l<sup>2</sup>C™ モジュール (マルチマスタ / スレーブをサポート)

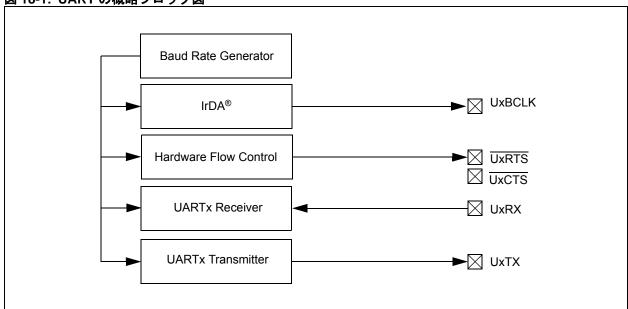

- 2 x UART モジュール (RS-485、RS-232、LIN/J2602、IrDA<sup>®</sup> をサポート)

- 5x16ビットタイマ/カウンタ (プログラマブルプリスケーラ付き)

- ペアで32ビットタイマ/カウンタとして使用可能

- 3 x 16 ビット キャプチャ入力 (専用タイマ付き)

- 3 x 16 ビット コンペア /PWM 出力 (専用タイマ付き)

- 設定可能なオープンドレイン出力(デジタル I/O ピン)

- 最大3x外部割り込み要因

### アナログ機能:

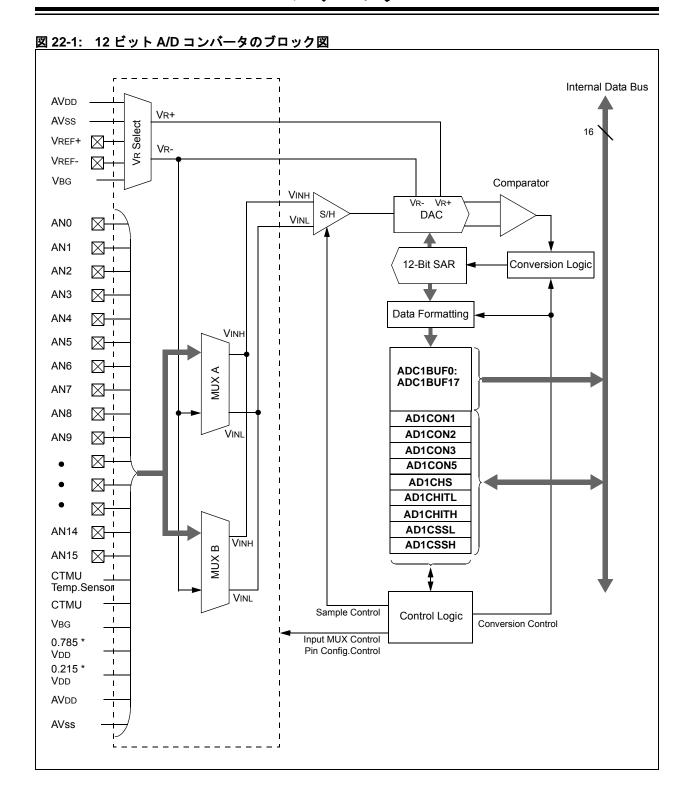

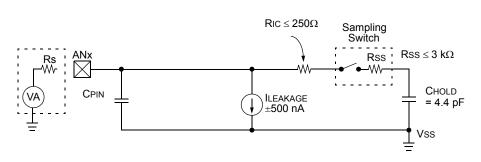

- 12 ビット アナログ / デジタル コンバータ (最大 16 チャンネル)

- 100 ksps の変換レート

- スリープ/アイドルモード時も変換可能

- スリープおよびアイドルモード時の自動サンプリング タイマ対応オプション

- 自動コンペアオプションによる復帰

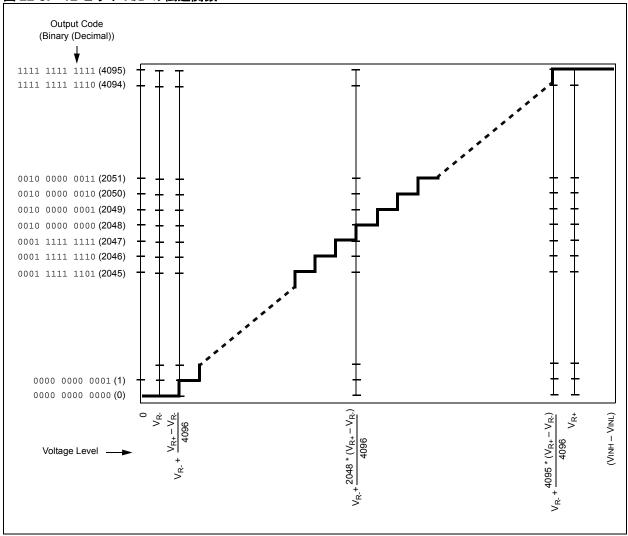

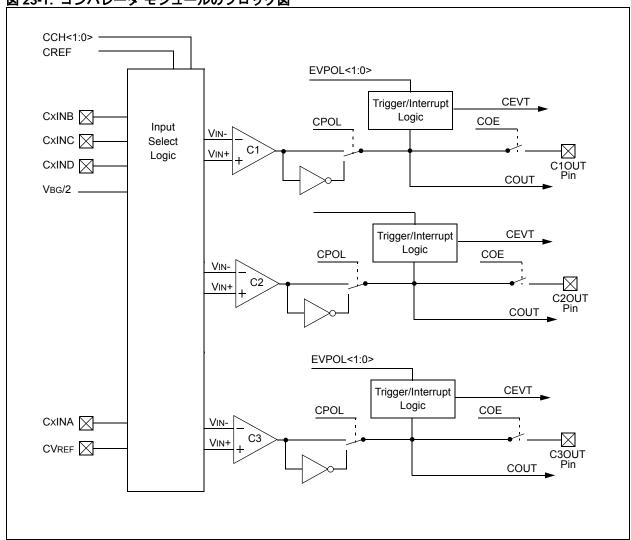

- 2xレールツーレールアナログコンパレータ (入出力コンフィグレーションはプログラマブル)

- 内蔵参照電圧

- ・ 内部温度センサ

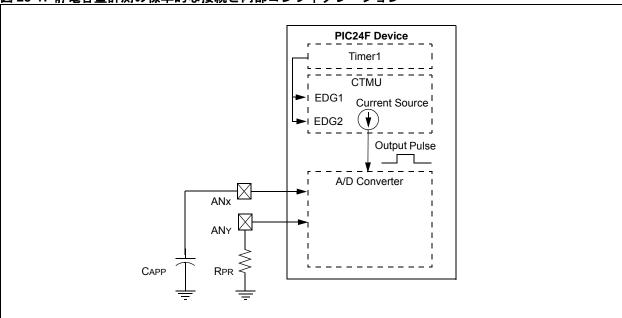

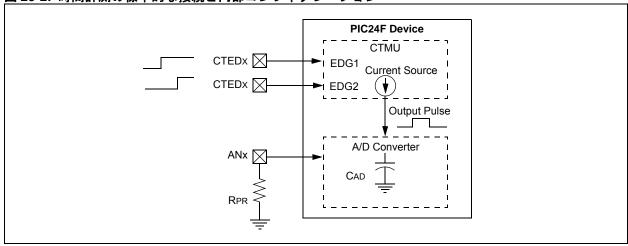

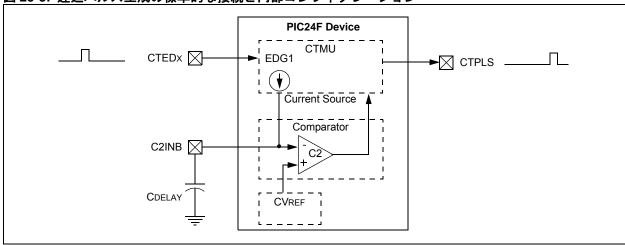

- 充電時間計測ユニット (CTMU)

- 静電容量計測 (16 チャンネル)

- 時間計測 (最高分解能: 200 ps)

- 遅延/パルス生成(最高分解能:1ns)

### その他の特殊なマイクロコントローラ機能:

- ・ 幅広い動作電圧レンジ

- 1.8 ~ 3.6 V (PIC24F デバイス)

- 2.0 ~ 5.5 V (PIC24FV デバイス)

- 低消費電力復帰要因とスーパーバイザ

- 超低消費電力復帰 (ULPWU);スリープ / ディープスリープ用

- 低消費電力 ウォッチドッグ タイマ (DSWDT); ディープスリープ用

- 外部低消費電カブラウンアウト リセット (DSBOR); ディープスリープ用;

- 他の全てのモードには LPBOR を使用

- システム周波数レンジ宣言ビット

- 周波数レンジの宣言による消費電流の最適化

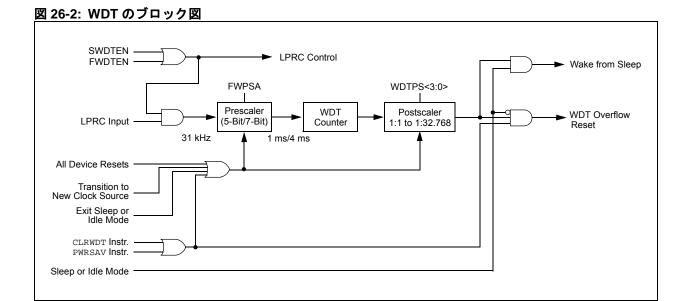

- 内蔵低消費電力 RC オシレータを使用する標準ウォッチドッグ タイマ (WDT) による高信頼性動作

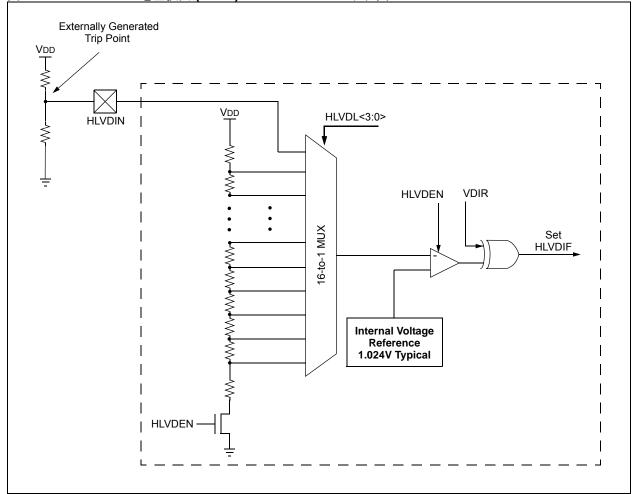

- プログラマブル HIGH/LOW 電圧検出 (HLVD)

- スリープ時に無効化可能な3点のプログラマブルトリップポイントを使用する標準ブラウンアウトリセット(BOR)

- 大電流シンク / ソース (18 mA/18 mA; 全 I/O ピンにて)

- ・ フラッシュ プログラムメモリ

- 消去/書き込みサイクル:10,000回以上

- データ保持期間:40年以上

- データ EEPROM

- 消去/書き込みサイクル: 100,000 回以上

- データ保持期間:40年以上

- ・ フェイルセーフ クロック監視機能

- プログラマブルな参照クロック出力

- ソフトウェア制御で自己書き込み可能

- In-Circuit Serial Programming™ (ICSP™) と 2 本のピン を介するインサーキット デバッグ (ICD)

|                                  |     | メモリ                      |                |                  |               |             | /PWM            |                              |     |                    | (ch)         |                 |            |      |

|----------------------------------|-----|--------------------------|----------------|------------------|---------------|-------------|-----------------|------------------------------|-----|--------------------|--------------|-----------------|------------|------|

| PIC24F<br>デバイス                   | ピン数 | フラッシュ<br>プログラム<br>(byte) | SRAM<br>(byte) | EE データ<br>(byte) | タイマ<br>16 ピット | キャプチャ<br>入力 | カコンペア /PV<br>出力 | UART<br>IrDA <sup>®</sup> 付き | IdS | I <sup>2</sup> Стм | 12 ピット A/D ( | <b>ダー</b> つ》/ヘロ | (стми (сь) | RTCC |

| PIC24FV08KA101<br>/PIC24F16KA301 | 20  | 16K                      | 2K             | 512              | 5             | 3           | 3               | 2                            | 2   | 2                  | 12           | 3               | 12         | Υ    |

| PIC24FV16KA101<br>/PIC24F32KA301 | 20  | 32K                      | 2K             | 512              | 5             | 3           | 3               | 2                            | 2   | 2                  | 12           | 3               | 12         | Υ    |

| PIC24FV08KA102<br>/PIC24F16KA302 | 28  | 16K                      | 2K             | 512              | 5             | 3           | 3               | 2                            | 2   | 2                  | 13           | 3               | 13         | Υ    |

| PIC24FV16KA102<br>/PIC24F32KA302 | 28  | 32K                      | 2K             | 512              | 5             | 3           | 3               | 2                            | 2   | 2                  | 13           | 3               | 13         | Υ    |

| PIC24FV16GA004<br>/PIC24F16KA304 | 44  | 16K                      | 2K             | 512              | 5             | 3           | 3               | 2                            | 2   | 2                  | 16           | 3               | 16         | Y    |

| PIC24FV32GA004<br>/PIC24F32KA304 | 44  | 32K                      | 2K             | 512              | 5             | 3           | 3               | 2                            | 2   | 2                  | 16           | 3               | 16         | Y    |

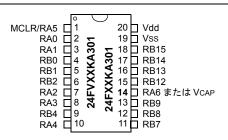

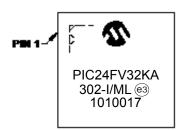

### ピン配置図

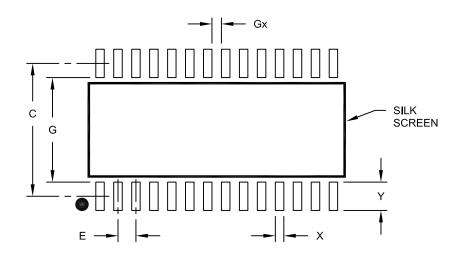

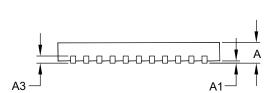

### 20 ピン SPDIP/SSOP/SOIC(1)

|    | ť٤                                                                | 機能                                                                |

|----|-------------------------------------------------------------------|-------------------------------------------------------------------|

| ピン | PIC24FVXXKA301                                                    | PIC24FXXKA301                                                     |

| 1  | MCLR/Vpp/RA5                                                      | MCLR/Vpp/RA5                                                      |

| 2  | PGEC2/VREF+/CVREF+/AN0/C3INC/SCK2/CN2/RA0                         | PGEC2/VREF+/CVREF+/AN0/C3INC/SCK2/CN2/RA0                         |

| 3  | PGED2/CVREF-/VREF-/AN1/SDO2/CN3/RA1                               | PGED2/CVREF-/VREF-/AN1/SDO2/CN3/RA1                               |

| 4  | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/SDI2/<br>OC2/CN4/RB0 | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/SDI2/<br>OC2/CN4/RB0 |

| 5  | PGEC1/AN3/C1INC/C2INA/U2RX/OC3/CTED12/CN5/RB1                     | PGEC1/AN3/C1INC/C2INA/U2RX/OC3/CTED12/CN5/RB1                     |

| 6  | AN4/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2                            | AN4/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2                            |

| 7  | OSCI/AN13/C1INB/C2IND/CLKI/CN30/RA2                               | OSCI/AN13/C1INB/C2IND/CLKI/CN30/RA2                               |

| 8  | OSCO/AN14/C1INA/C2INC/CLKO/CN29/RA3                               | OSCO/AN14/C1INA/C2INC/CLKO/CN29/RA3                               |

| 9  | PGED3/SOSCI/AN15/U2RTS/CN1/RB4                                    | PGED3/SOSCI/AN15/U2RTS/CN1/RB4                                    |

| 10 | PGEC3/SOSCO/SCLKI/U2CTS/CN0/RA4                                   | PGEC3/SOSCO/SCLKI/U2CTS/CN0/RA4                                   |

| 11 | U1TX/C2OUT/OC1/IC1/CTED1/INT0/CN23/RB7                            | U1TX/INT0/CN23/RB7                                                |

| 12 | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                                  | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                                  |

| 13 | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                                | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                                |

| 14 | VCAP                                                              | C2OUT/OC1/IC1/CTED1/INT2/CN8/RA6                                  |

| 15 | AN12/LVDIN/SCK1/SS2/IC3/CTED2/INT2/CN14/RB12                      | AN12/LVDIN/SCK1/SS2/IC3/CTED2/CN14/RB12                           |

| 16 | AN11/SDO1/OCFB/CTPLS/CN13/RB13                                    | AN11/SDO1/OCFB/CTPLS/CN13/RB13                                    |

| 17 | CVREF/AN10/C3INB/RTCC/SDI1/C1OUT/OCFA/CTED5/INT1/<br>CN12/RB14    | CVREF/AN10/C3INB/RTCC/SDI1/C1OUT/OCFA/CTED5/INT1/<br>CN12/RB14    |

| 18 | AN9/C3INA/SCL2/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15                 | AN9/C3INA/SCL2/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15                 |

| 19 | Vss/AVss                                                          | Vss/AVss                                                          |

| 20 | VDD/AVDD                                                          | VDD/AVDD                                                          |

**Note 1: 太字**のピン番号は、PIC24FV と PIC24F でピン機能が異なる事を意味します。 **Note 1:** PIC24FJ64GA ファミリのピンの最大電圧は 3.6 V であり、5 V を許容しません。

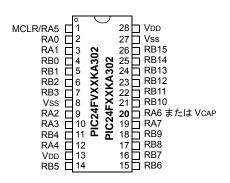

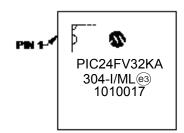

### ピン配置図

### 28 ピン SPDIP/SSOP/SOIC(1,2)

|    | ピン                                                    | 幾能                                                        |

|----|-------------------------------------------------------|-----------------------------------------------------------|

| ピン | PIC24FVXXKA302                                        | PIC24FXXKA302                                             |

| 1  | MCLR/Vpp/RA5                                          | MCLR/Vpp/RA5                                              |

| 2  | VREF+/CVREF+/AN0/C3INC/CTED1/CN2/RA0                  | VREF+/CVREF+/AN0/C3INC/CTED1/CN2/RA0                      |

| 3  | CVREF-/VREF-/AN1/CN3/RA1                              | CVREF-/VREF-/AN1/CN3/RA1                                  |

| 4  | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/CN4/RB0  | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/CN4/RB0      |

| 5  | PGEC1/AN3/C1INC/C2INA/U2RX/CTED12/CN5/RB1             | PGEC1/AN3/C1INC/C2INA/U2RX/CTED12/CN5/RB1                 |

| 6  | AN4/C1INB/C2IND/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2    | AN4/C1INB/C2IND/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2        |

| 7  | AN5/C1INA/C2INC/SCL2/CN7/RB3                          | AN5/C1INA/C2INC/SCL2/CN7/RB3                              |

| 8  | Vss                                                   | Vss                                                       |

| 9  | OSCI/AN13/CLKI/CN30/RA2                               | OSCI/AN13/CLKI/CN30/RA2                                   |

| 10 | OSCO/AN14/CLKO/CN29/RA3                               | OSCO/AN14/CLKO/CN29/RA3                                   |

| 11 | SOSCI/AN15/U2RTS/CN1/RB4                              | SOSCI/AN15/U2RTS/CN1/RB4                                  |

| 12 | SOSCO/SCLKI/U2CTS/CN0/RA4                             | SOSCO/SCLKI/U2CTS/CN0/RA4                                 |

| 13 | VDD                                                   | VDD                                                       |

| 14 | PGED3/ASDA <sup>(1)</sup> /SCK2/CN27/RB5              | PGED3/ASDA <sup>(1)</sup> /SCK2/CN27/RB5                  |

| 15 | PGEC3/ASCL <sup>(1)</sup> /SDO2/CN24/RB6              | PGEC3/ASCL <sup>(1)</sup> /SDO2/CN24/RB6                  |

| 16 | U1TX/C2OUT/OC1/INT0/CN23/RB7                          | U1TX/INT0/CN23/RB7                                        |

| 17 | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                      | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                          |

| 18 | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                    | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                        |

| 19 | SDI2/IC1/CTED3/CN9/RA7                                | SDI2/IC1/CTED3/CN9/RA7                                    |

| 20 | VCAP                                                  | C2OUT/OC1/CTED1/INT2/CN8/RA6                              |

| 21 | PGED2/SDI1/OC3/CTED11/CN16/RB10                       | PGED2/SDI1/OC3/CTED11/CN16/RB10                           |

| 22 | PGEC2/SCK1/OC2/CTED9/CN15/RB11                        | PGEC2/SCK1/OC2/CTED9/CN15/RB11                            |

| 23 | AN12/LVDIN/SS2/IC3/CTED2/INT2/CN14/RB12               | AN12/LVDIN/SS2/IC3/CTED2/CN14/RB12                        |

| 24 | AN11/SDO1/OCFB/CTPLS/CN13/RB13                        | AN11/SDO1/OCFB/CTPLS/CN13/RB13                            |

| 25 | CVREF/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/RB14 | CVREF/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 |

| 26 | AN9/C3INA/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15          | AN9/C3INA/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15              |

| 27 | Vss/AVss                                              | Vss/AVss                                                  |

| 28 | VDD/AVDD                                              | VDD/AVDD                                                  |

**凡例**: 太字のピン番号は、PIC24FV と PIC24F でピン機能が異なる事を意味します。

Note 1: I2CSEL コンフィグレーション ビットは、SDA1/ASDA1 と SCL1 /ASCL1 のピンペアを選択します。

2: PIC24FJ64GA ファミリのピンの最大電圧は 3.6 V であり、5 V を許容しません。

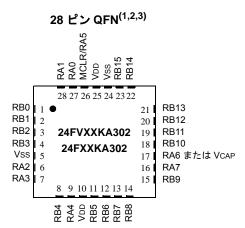

### ピン配置図

|    | ピン機能                                                      |                                                           |  |  |  |  |  |  |  |  |  |

|----|-----------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| ピン | PIC24FVXXKA302                                            | PIC24FXXKA302                                             |  |  |  |  |  |  |  |  |  |

| 1  | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/CN4/RB0      | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/CN4/RB0      |  |  |  |  |  |  |  |  |  |

| 2  | PGEC1/AN3/C1INC/C2INA/U2RX/CTED12/CN5/RB1                 | PGEC1/AN3/C1INC/C2INA/U2RX/CTED12/CN5/RB1                 |  |  |  |  |  |  |  |  |  |

| 3  | AN4/C1INB/C2IND/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2        | AN4/C1INB/C2IND/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2        |  |  |  |  |  |  |  |  |  |

| 4  | AN5/C1INA/C2INC/SCL2/CN7/RB3                              | AN5/C1INA/C2INC/SCL2/CN7/RB3                              |  |  |  |  |  |  |  |  |  |

| 5  | Vss                                                       | Vss                                                       |  |  |  |  |  |  |  |  |  |

| 6  | OSCI/AN13/CLKI/CN30/RA2                                   | OSCI/AN13/CLKI/CN30/RA2                                   |  |  |  |  |  |  |  |  |  |

| 7  | OSCO/AN14/CLKO/CN29/RA3                                   | OSCO/AN14/CLKO/CN29/RA3                                   |  |  |  |  |  |  |  |  |  |

| 8  | SOSCI/AN15/U2RTS/CN1/RB4                                  | SOSCI/AN15/U2RTS/CN1/RB4                                  |  |  |  |  |  |  |  |  |  |

| 9  | SOSCO/SCLKI/U2CTS/CN0/RA4                                 | SOSCO/SCLKI/U2CTS/CN0/RA4                                 |  |  |  |  |  |  |  |  |  |

| 10 | VDD                                                       | VDD                                                       |  |  |  |  |  |  |  |  |  |

| 11 | PGED3/ASDA1 <sup>(2)</sup> /SCK2/CN27/RB5                 | PGED3/ASDA1 <sup>(2)</sup> /SCK2/CN27/RB5                 |  |  |  |  |  |  |  |  |  |

| 12 | PGEC3/ASCL1 <sup>(2)</sup> /SDO2/CN24/RB6                 | PGEC3/ASCL1 <sup>(2)</sup> /SDO2/CN24/RB6                 |  |  |  |  |  |  |  |  |  |

| 13 | U1TX/C2OUT/OC1/INT0/CN23/RB7                              | U1TX/INT0/CN23/RB7                                        |  |  |  |  |  |  |  |  |  |

| 14 | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                          | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                          |  |  |  |  |  |  |  |  |  |

| 15 | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                        | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                        |  |  |  |  |  |  |  |  |  |

| 16 | SDI2/IC1/CTED3/CN9/RA7                                    | SDI2/IC1/CTED3/CN9/RA7                                    |  |  |  |  |  |  |  |  |  |

| 17 | VCAP                                                      | C2OUT/OC1/CTED1/INT2/CN8/RA6                              |  |  |  |  |  |  |  |  |  |

| 18 | PGED2/SDI1/OC3/CTED11/CN16/RB10                           | PGED2/SDI1/OC3/CTED11/CN16/RB10                           |  |  |  |  |  |  |  |  |  |

| 19 | PGEC2/SCK1/OC2/CTED9/CN15/RB11                            | PGEC2/SCK1/OC2/CTED9/CN15/RB11                            |  |  |  |  |  |  |  |  |  |

| 20 | AN12/LVDIN/SS2/IC3/CTED2/INT2/CN14/RB12                   | AN12/LVDIN/SS2/IC3/CTED2/CN14/RB12                        |  |  |  |  |  |  |  |  |  |

| 21 | AN11/SDO1/OCFB/CTPLS/CN13/RB13                            | AN11/SDO1/OCFB/CTPLS/CN13/RB13                            |  |  |  |  |  |  |  |  |  |

| 22 | CVREF/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 | CVREF/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 |  |  |  |  |  |  |  |  |  |

| 23 | AN9/C3INA/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15              | AN9/C3INA/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15              |  |  |  |  |  |  |  |  |  |

| 24 | Vss/AVss                                                  | Vss/AVss                                                  |  |  |  |  |  |  |  |  |  |

| 25 | VDD/AVDD                                                  | VDD/AVDD                                                  |  |  |  |  |  |  |  |  |  |

| 26 | MCLR/Vpp/RA5                                              | MCLR/Vpp/RA5                                              |  |  |  |  |  |  |  |  |  |

| 27 | VREF+/CVREF+/AN0/C3INC/CTED1/CN2/RA0                      | VREF+/CVREF+/AN0/C3INC/CTED1/CN2/RA0                      |  |  |  |  |  |  |  |  |  |

| 28 | CVRFF-/VRFF-/AN1/CN3/RA1                                  | CVREE-/VREE-/AN1/CN3/RA1                                  |  |  |  |  |  |  |  |  |  |

凡例: 太字のピン番号は、PIC24FVと PIC24Fでピン機能が異なる事を意味します。

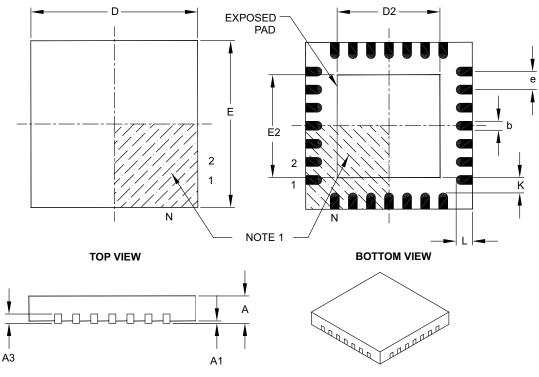

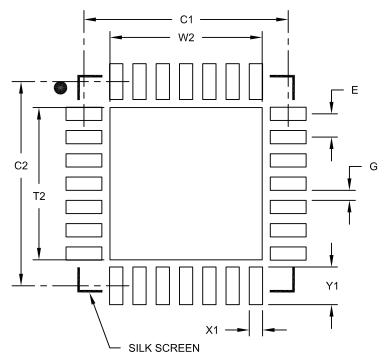

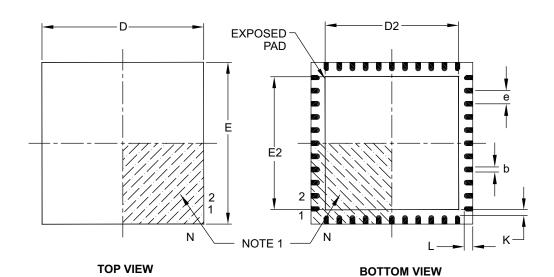

Note 1: デバイス下面の露出パッドは Vss に接続されています。

2: I2CSEL コンフィグレーション ビットは、SDA1/ASDA1 と SCL1 /ASCL1 のピンペアを選択します。

3: PIC24FJ64GA ファミリのピンの最大電圧は 3.6 V であり、5 V を許容しません。

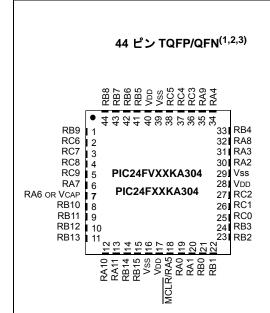

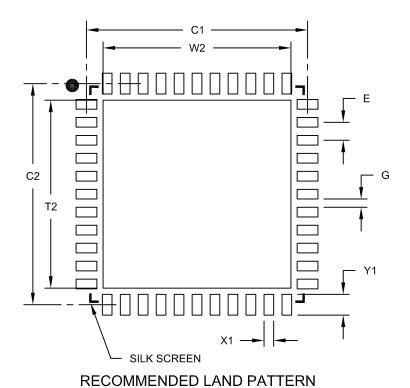

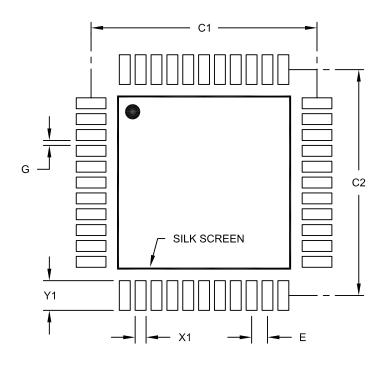

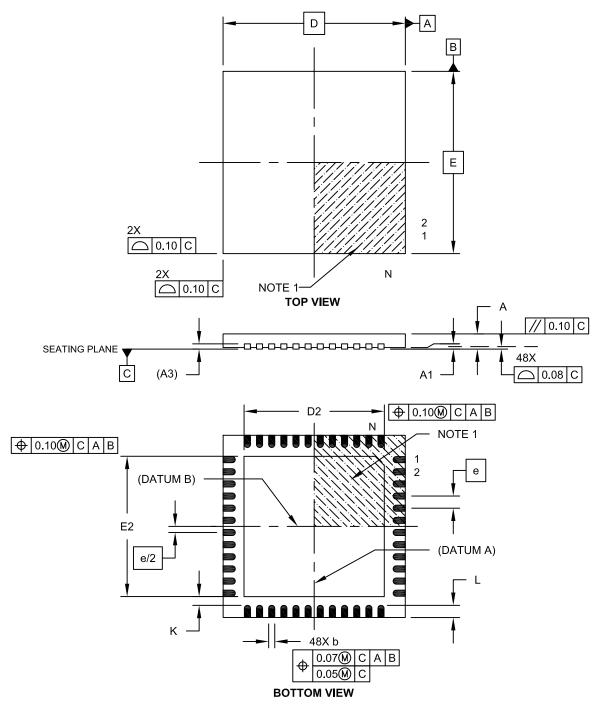

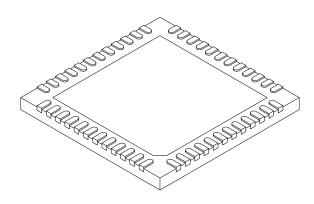

### ピン配置図

|          | 195                                                           | 146 Div                                                       |

|----------|---------------------------------------------------------------|---------------------------------------------------------------|

| ピン       | PIC24FVXXKA304                                                | ノ機能<br>PIC24FXXKA304                                          |

| 1        | SDA1/T1CK/U1RTS/CTED4/CN21/<br>RB9                            | SDA1/T1CK/U1RTS/CTED4/CN21/<br>RB9                            |

| 2        | U1RX/CN18/RC6                                                 | U1RX/CN18/RC6                                                 |

| 3        | U1TX/CN17/RC7                                                 | U1TX/CN17/RC7                                                 |

| 4        | OC2/CN20/RC8                                                  | OC2/CN20/RC8                                                  |

| 5        | IC2/CTED7/CN19/RC9                                            | IC2/CTED7/CN19/RC9                                            |

| 6        | IC1/CTED3/CN9/RA7                                             | IC1/CTED3/CN9/RA7                                             |

| 7        | VCAP                                                          | C2OUT/OC1/CTED1/INT2/CN8/RA6                                  |

| 8        | PGED2/SDI1/CTED11/CN16/RB10                                   | PGED2/SDI1/CTED11/CN16/RB10                                   |

| 9        | PGEC2/SCK1/CTED9/CN15/RB11                                    | PGEC2/SCK1/CTED9/CN15/RB11                                    |

| 10       | AN12/LVDIN/CTED2/INT2/CN14/<br>RB12                           | AN12/LVDIN/CTED2/CN14/RB12                                    |

| 11       | AN11/SDO1/CTPLS/CN13/RB13                                     | AN11/SDO1/CTPLS/CN13/RB13                                     |

| 12       | OC3/CN35/RA10                                                 | OC3/CN35/RA10                                                 |

| 13       | IC3/CTED8/CN36/RA11                                           | IC3/CTED8/CN36/RA11                                           |

| 14       | CVREF/AN10/C3INB/RTCC/<br>C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 | CVREF/AN10/C3INB/RTCC/<br>C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 |

| 15       | AN9/C3INA/T3CK/T2CK/REFO/<br>SS1/CTED6/CN11/RB15              | AN9/C3INA/T3CK/T2CK/REFO/<br>SS1/CTED6/CN11/RB15              |

| 16       | Vss/AVss                                                      | Vss/AVss                                                      |

| 17       | VDD/AVDD                                                      | VDD/AVDD                                                      |

| 18       | MCLR/Vpp/RA5                                                  | MCLR/VPP/RA5                                                  |

| 19       | VREF+/CVREF+/AN0/C3INC/<br>CTED1/CN2/RA0                      | VREF+/CVREF+/AN0/C3INC/CN2/<br>RA0                            |

| 20       | CVREF-/VREF-/AN1/CN3/RA1                                      | CVREF-/VREF-/AN1/CN3/RA1                                      |

| 21       | PGED1/AN2/ULPWU/CTCMP/<br>C1IND/C2INB/C3IND/U2TX/CN4/RB0      | PGED1/AN2/ULPWU/CTCMP/C1IND/<br>C2INB/C3IND/U2TX/CN4/RB0      |

| 22       | PGEC1/AN3/C1INC/C2INA/U2RX/<br>CTED12/CN5/RB1                 | PGEC1/AN3/C1INC/C2INA/U2RX/<br>CTED12/CN5/RB1                 |

| 23       | AN4/C1INB/C2IND/SDA2/T5CK/<br>T4CK/CTED13/CN6/RB2             | AN4/C1INB/C2IND/SDA2/T5CK/<br>T4CK/CTED13/CN6/RB2             |

| 24       | AN5/C1INA/C2INC/SCL2/CN7/<br>RB3                              | AN5/C1INA/C2INC/SCL2/CN7/RB3                                  |

| 25       | AN6/CN32/RC0                                                  | AN6/CN32/RC0                                                  |

| 26       | AN7/CN31/RC1                                                  | AN7/CN31/RC1                                                  |

| 27       | AN8/CN10/RC2                                                  | AN8/CN10/RC2                                                  |

| 28       | VDD                                                           | VDD                                                           |

| 29       | Vss                                                           | Vss                                                           |

| 30       | OSCI/AN13/CLKI/CN30/RA2                                       | OSCI/AN13/CLKI/CN30/RA2                                       |

| 31       | OSCO/AN14/CLKO/CN29/RA3                                       | OSCO/AN14/CLKO/CN29/RA3                                       |

| 32       | OCFB/CN33/RA8                                                 | OCFB/CN33/RA8                                                 |

| 33       | SOSCI/AN15/U2RTS/CN1/RB4                                      | SOSCI/AN15/U2RTS/CN1/RB4                                      |

| 34       | SOSCO/SCLKI/U2CTS/CN0/RA4                                     | SOSCO/SCLKI/U2CTS/CN0/RA4                                     |

| 35       | SS2/CN34/RA9                                                  | SS2/CN34/RA9                                                  |

| 36       | SDI2/CN28/RC3                                                 | SDI2/CN28/RC3                                                 |

| 37       | SDO2/CN25/RC4                                                 | SDO2/CN25/RC4                                                 |

| 38       | SCK2/CN26/RC5                                                 | SCK2/CN26/RC5                                                 |

| 39       | Vss                                                           | Vss                                                           |

| 40       | VDD<br>PGED3/ASDA1 <sup>(2)</sup> /CN27/RB5                   | VDD<br>PGED3/ASDA1 <sup>(2)</sup> /CN27/RB5                   |

| 41<br>42 | PGEC3/ASDA1(-*/CN27/RB5) PGEC3/ASCL1(2)/CN24/RB6              | PGEC3/ASDA1\*-/CN2//RB5                                       |

| 43       | INT0/CN23/RB7                                                 | INTO/CN23/RB7                                                 |

| 44       | SCL1/U1CTS/C3OUT/CTED10/<br>CN22/RB8                          | SCL1/U1CTS/C3OUT/CTED10/<br>CN22/RB8                          |

**凡例**: 太字のピン番号は、PIC24FV と PIC24F でピン機能が異なる事を意味します。

Note 1: デバイス下面の露出パッドはVssに接続されています。

2: I2CSEL コンフィグレーション ビット は、SDA1/ASDA1 と SCL1 /ASCL1 のピ ンペアを選択します。

3: PIC24FJ64GA ファミリのピンの最大電 圧は 3.6 V であり、5 V を許容しません。

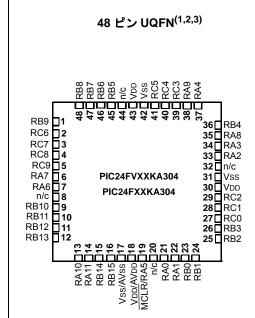

### ピン配置図

|    | ピン様                                                      |                                                        |  |  |  |  |  |  |

|----|----------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|--|

| ピン | PIC24FVXXKA304                                           | PIC24FXXKA304                                          |  |  |  |  |  |  |

| 1  | SDA1/T1CK/U1RTS/CTED4/CN21/RB9                           | SDA1/T1CK/U1RTS/CTED4/CN21<br>RB9                      |  |  |  |  |  |  |

| 2  | U1RX/CN18/RC6                                            | U1RX/CN18/RC6                                          |  |  |  |  |  |  |

| 3  | U1TX/CN17/RC7                                            | U1TX/CN17/RC7                                          |  |  |  |  |  |  |

| 4  | OC2/CN20/RC8                                             | OC2/CN20/RC8                                           |  |  |  |  |  |  |

| 5  | IC2/CTED7/CN19/RC9                                       | IC2/CTED7/CN19/RC9                                     |  |  |  |  |  |  |

| 6  | IC1/CTED3/CN9/RA7                                        | IC1/CTED3/CN9/RA7                                      |  |  |  |  |  |  |

| 7  | VCAP                                                     | INT2/RA6                                               |  |  |  |  |  |  |

| 8  | n/c                                                      | n/c                                                    |  |  |  |  |  |  |

| 9  | PGED2/SDI1/CTED11/CN16/RB10                              | PGED2/SDI1/CTED11/CN16/RB10                            |  |  |  |  |  |  |

| 10 | PGEC2/SCK1/CTED9/CN15/RB11                               | PGEC2/SCK1/CTED9/CN15/RB11                             |  |  |  |  |  |  |

| 11 | AN12/LVDIN/CTED2/INT2/CN14/RB12                          | AN12/LVDIN/CTED2/CN14/RB12                             |  |  |  |  |  |  |

| 12 | AN11/SDO1/CTPLS/CN13/RB13                                | AN11/SDO1/CTPLS/CN13/RB13                              |  |  |  |  |  |  |

| 13 | OC3/CN35/RA10                                            | OC3/CN35/RA10                                          |  |  |  |  |  |  |

| 14 | IC3/CTED8/CN36/RA11                                      | IC3/CTED8/CN36/RA11                                    |  |  |  |  |  |  |

| 15 | CVREF/AN10/C3INB/RTCC/                                   | CVREF/AN10/C3INB/RTCC/C1OUT                            |  |  |  |  |  |  |

| 16 | C1OUT/OCFA/CTED5/INT1/CN12/RB14                          | OCFA/CTED5/INT1/CN12/RB14                              |  |  |  |  |  |  |

| 16 | AN9/C3INA/T3CK/T2CK/REFO/<br>SS1/CTED6/CN11/RB15         | AN9/C3INA/T3CK/T2CK/REFO/<br>SS1/CTED6/CN11/RB15       |  |  |  |  |  |  |

| 17 | Vss/AVss                                                 | Vss/AVss                                               |  |  |  |  |  |  |

| 18 | VDD/AVDD                                                 | VDD/AVDD                                               |  |  |  |  |  |  |

| 19 | MCLR/RA5                                                 | MCLR/RA5                                               |  |  |  |  |  |  |

| 20 | n/c                                                      | n/c                                                    |  |  |  |  |  |  |

| 21 | VREF+/CVREF+/AN0/C3INC/<br>CTED1/CN2/RA0                 | VREF+/CVREF+/AN0/C3INC/<br>CTED1/CN2/RA0               |  |  |  |  |  |  |

| 22 | CVREF-/VREF-/AN1/CN3/RA1                                 | CVREF-/VREF-/AN1/CN3/RA1                               |  |  |  |  |  |  |

| 23 | PGED1/AN2/ULPWU/CTCMP/C1IND/<br>C2INB/C3IND/U2TX/CN4/RB0 | PGED1/AN2/ULPWU/CTCMP/C1IN<br>C2INB/C3IND/U2TX/CN4/RB0 |  |  |  |  |  |  |

| 24 | PGEC1/AN3/C1INC/C2INA/U2RX/<br>CTED12/CN5/RB1            | PGEC1/AN3/C1INC/C2INA/U2RX<br>CTED12/CN5/RB1           |  |  |  |  |  |  |

| 25 | AN4/C1INB/C2IND/SDA2/T5CK/<br>T4CK/CTED13/CN6/RB2        | AN4/C1INB/C2IND/SDA2/T5CK/<br>T4CK/CTED13/CN6/RB2      |  |  |  |  |  |  |

| 26 | AN5/C1INA/C2INC/SCL2/CN7/RB3                             | AN5/C1INA/C2INC/SCL2/CN7/RB                            |  |  |  |  |  |  |

| 27 | AN6/CN32/RC0                                             | AN6/CN32/RC0                                           |  |  |  |  |  |  |

| 28 | AN7/CN31/RC1                                             | AN7/CN31/RC1                                           |  |  |  |  |  |  |

| 29 | AN8/CN10/RC2                                             | AN8/CN10/RC2                                           |  |  |  |  |  |  |

| 30 | VDD                                                      | VDD                                                    |  |  |  |  |  |  |

| 31 | Vss                                                      | Vss                                                    |  |  |  |  |  |  |

| 32 | n/c                                                      | n/c                                                    |  |  |  |  |  |  |

| 33 | OSCI/AN13/CLKI/CN30/RA2                                  | OSCI/AN13/CLKI/CN30/RA2                                |  |  |  |  |  |  |

| 34 | OSCO/AN14/CLKO/CN29/RA3                                  | OSCO/AN14/CLKO/CN29/RA3                                |  |  |  |  |  |  |

| 35 | OCFB/CN33/RA8                                            | OCFB/CN33/RA8                                          |  |  |  |  |  |  |

| 36 | SOSCI/AN15/U2RTS/CN1/RB4                                 | SOSCI/AN15/U2RTS/CN1/RB4                               |  |  |  |  |  |  |

| 37 | SOSCO/SCLKI/U2CTS/CN0/RA4                                | SOSCO/SCLKI/U2CTS/CN0/RA4                              |  |  |  |  |  |  |

| 38 | SS2/CN34/RA9                                             | SS2/CN34/RA9                                           |  |  |  |  |  |  |

| 39 | SDI2/CN28/RC3                                            | SDI2/CN28/RC3                                          |  |  |  |  |  |  |

| 40 | SDO2/CN25/RC4                                            | SDO2/CN25/RC4                                          |  |  |  |  |  |  |

| 41 | SCK2/CN26/RC5                                            | SCK2/CN26/RC5                                          |  |  |  |  |  |  |

| 42 | Vss                                                      | Vss                                                    |  |  |  |  |  |  |

| 43 | VDD                                                      | VDD                                                    |  |  |  |  |  |  |

| 44 | n/c                                                      | n/c                                                    |  |  |  |  |  |  |

| 45 | PGED3/ASDA1 <sup>(2)</sup> /CN27/RB5                     | PGED3/ASDA1 <sup>(2)</sup> /CN27/RB5                   |  |  |  |  |  |  |

| 46 | PGEC3/ASCL1 <sup>(2)</sup> /CN24/RB6                     | PGEC3/ASCL1 <sup>(2)</sup> /CN24/RB6                   |  |  |  |  |  |  |

| 47 | C2OUT/OC1/INT0/CN23/RB7                                  | C2OUT/OC1/INT0/CN23/RB7                                |  |  |  |  |  |  |

| 48 | SCL1/U1CTS/C3OUT/CTED10/<br>CN22/RB8                     | SCL1/U1CTS/C3OUT/CTED10/<br>CN22/RB8                   |  |  |  |  |  |  |

**凡例**: 太字のピン番号は、PIC24FV と PIC24F でピン機能が異なる事を意味します。

Note 1: デバイス下面の露出パッドは Vss に接続されています。

2: I2CSEL コンフィグレーション ビットは、SDA1/ASDA1 と SCL1 /ASCL1 のピンペアを選択します。

**3:** PIC24F32KA3XX のピンの最大電圧は 3.6 V であり、5 V を許容しません。

### 目次

| 1.0        | デバイス概要                                             | 12  |

|------------|----------------------------------------------------|-----|

|            | ナハイ へ似安                                            |     |

| 2.0<br>3.0 | 16 ビット マイクロコントローラの使用にあたってのカイトライン                   |     |

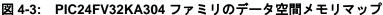

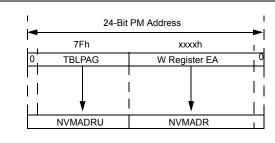

| 4.0        | メモリの構成                                             |     |

| 5.0        | フラッシュ プログラムメモリ                                     |     |

| 6.0        | データ EEPROM メモリ                                     |     |

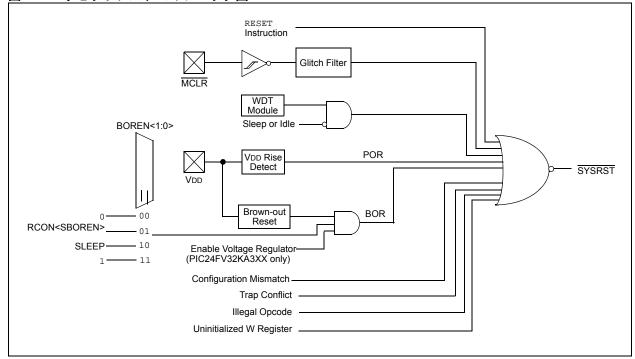

| 7.0        | リセット                                               |     |

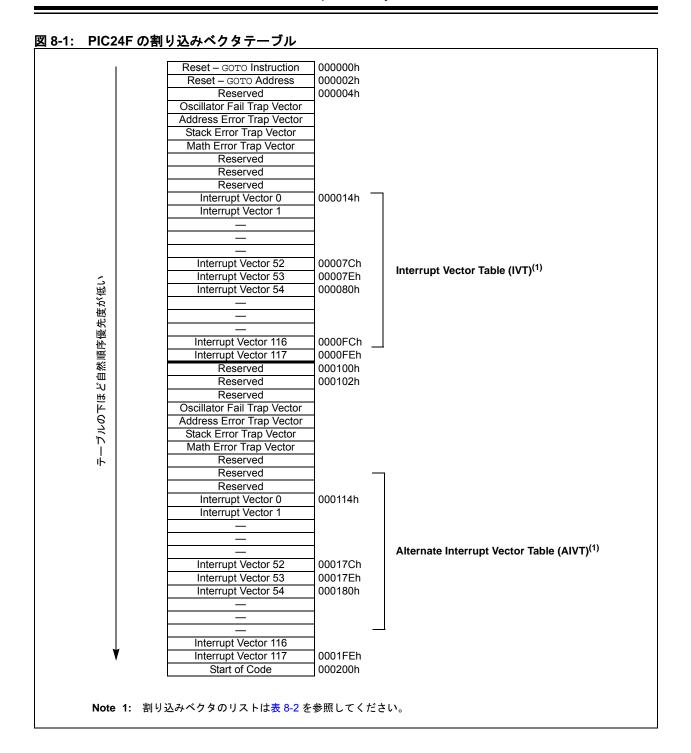

| 8.0        | 割り込みコントローラ                                         |     |

| 9.0        | オシレータ コンフィグレーション                                   |     |

| 10.0       |                                                    |     |

|            | 1/0 ポート                                            |     |

|            | Timer1                                             |     |

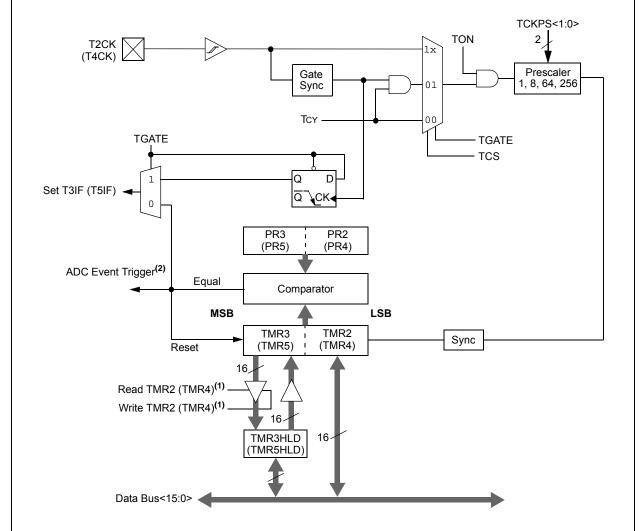

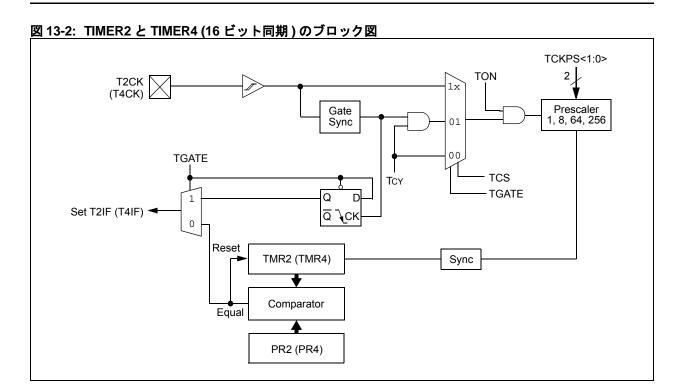

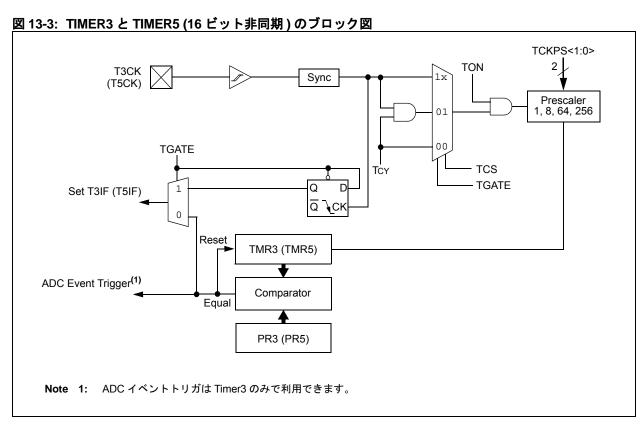

| 13.0       | Timer2/3 と Timer4/5                                | 145 |

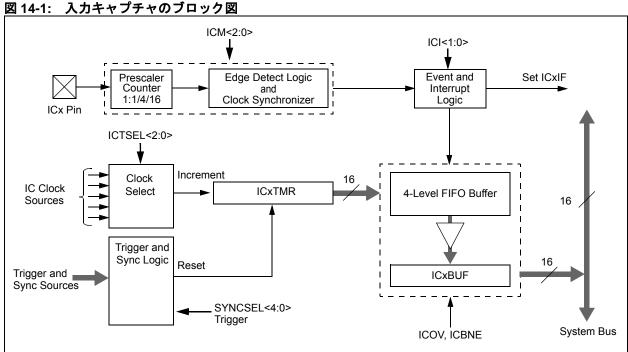

|            | 専用タイマを備えた入力キャプチャ                                   |     |

|            | 専用タイマを備えた出力コンペア                                    |     |

|            | シリアル ペリフェラル インターフェイス (SPI)                         |     |

| 17.0       | I <sup>2</sup> C™ (Inter-Integrated Circuit™)      | 173 |

| 18.0       | UART (Universal Asynchronous Receiver Transmitter) | 181 |

| 19.0       | リアルタイム クロック / カレンダ (RTCC)                          | 189 |

| 20.0       | 32 ビット プログラマブル巡回冗長検査 (CRC) ジェネレータ                  | 203 |

| 21.0       | HIGH/LOW 電圧検出 (HLVD)                               | 209 |

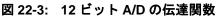

| 22.0       | しきい値検出機能を備えた 12 ビット A/D コンバータ                      | 211 |

| 23.0       | コンパレータ モジュール                                       | 225 |

|            | コンパレータ参照電圧                                         |     |

|            | 充電時間計測ユニット (CTMU)                                  |     |

| 26.0       | その他の特殊機能                                           | 239 |

| 27.0       | 開発サポート                                             | 251 |

| 28.0       | 命令セットの要約                                           | 255 |

|            | 電気的特性                                              |     |

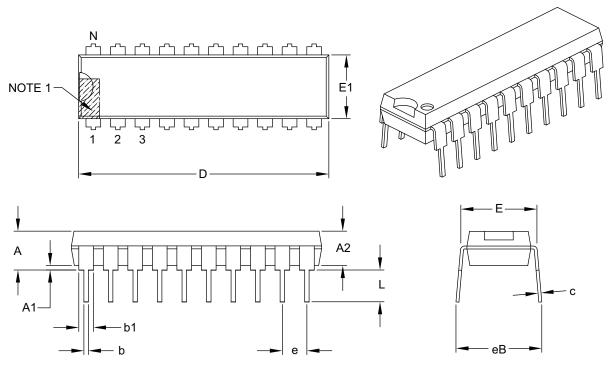

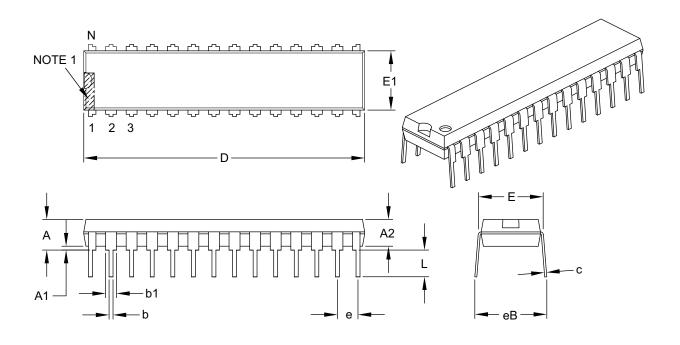

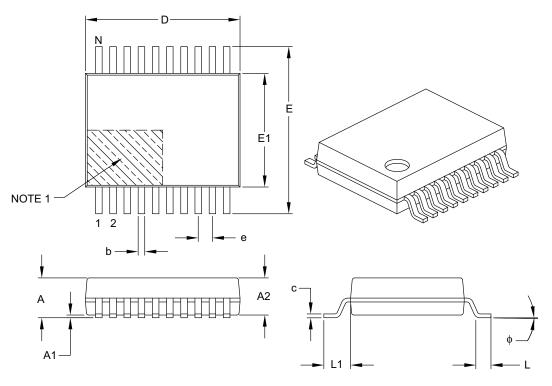

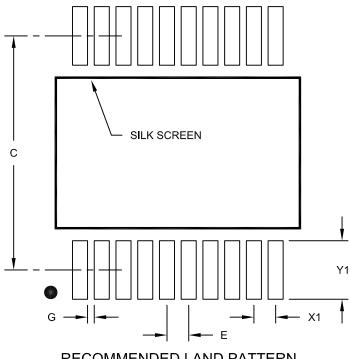

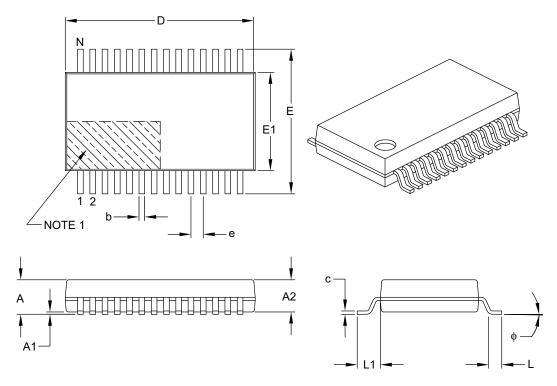

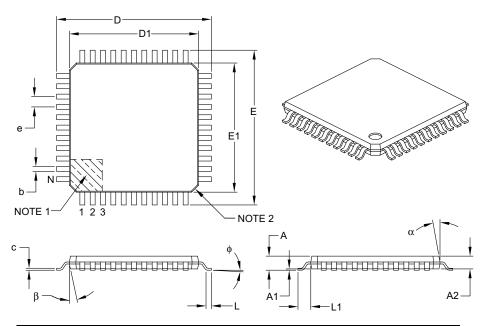

|            | パッケージ情報                                            |     |

| 補遺         |                                                    |     |

|            | クロチップ社ウェブサイト                                       |     |

|            | 変更通知サービス                                           |     |

|            | サポート                                               |     |

|            | アンケート                                              |     |

| 制口         | <b>悪別シュフ テ /</b> .                                 | 215 |

### 大切なお客様へ

マイクロチップ社は、弊社製品を存分にご活用頂くために、文書の作成に最善の努力を尽くしています。このため、弊社はお客 様のニーズにより的確にお応えできるように、継続的に文書の改善に努めて参ります。弊社は新刊、更新版をリリースする際に 内容の見直しと充実を図って参ります。

本書に関してご質問、ご意見をお持ちのお客様は、メール (docerrors@microchip.com) にて、あるいは本データシート巻末の 「読者アンケート」にご記入の上ファックス ((480)792-4150)にてお知らせください。お客様からのご感想をお待ちしております。

### 最新のデータシート

本データシートの最新版を入手するには、下記のウェブサイトで登録手続きを行ってください。

#### http://www.microchip.com

データシートのバージョンは、各ページの欄外下隅に記載されている文書番号で確認できます。文書番号の末尾文字がバージョ ン番号を表します (例: DS30000A\_JP であれば文書 DS30000\_JP のバージョン A)。

#### エラッタ

現行デバイスの動作とデータシート上の動作との間に微細な差違が生じた場合、その相違点と推奨対応策を記載したエラッタ シートを発行する場合があります。弊社は、デバイスや文書に関する問題を認識した時点でエラッタを発行します。エラッタに は、該当するシリコンと文書のリビジョンを明記しています。

ご使用のデバイス向けにエラッタシートが存在するかどうかは、以下の方法で確認できます。

- マイクロチップ社のウェブサイト; http://www.microchip.com

最寄のマイクロチップ社営業所(本書の最終ページ参照)

お問い合わせになる際は、ご使用のデバイスおよびシリコンとデータシートのリビジョン(文書番号含む)をお知らせください。

### 顧客変更通知システム

弊社ウェブサイト (www.microchip.com) でご登録頂くと、弊社の全製品に関する最新情報をお受け取り頂けます。

NOTE:

### 1.0 デバイスの概要

本データシートには、下記の各デバイスに関する情報 を記載しています。

- PIC24FV16KA301、PIC24F16KA301

- PIC24FV16KA302、PIC24F16KA302

- PIC24FV16KA304、PIC24F16KA304

- PIC24FV32KA301、PIC24F32KA301

- PIC24FV32KA302、PIC24F32KA302

- PIC24FV32KA304、PIC24F32KA304

マイクロチップ社の超低消費電力デバイスの新製品ラインである PIC24FV32KA304 ファミリは、豊富な周辺モジュール機能セットと拡張された計算性能を備えた 16 ビット マイクロコントローラ ファミリです。このファミリは、8 ビット プラットフォームからのアップグレードは必要であるものの、デジタルシグナルコントローラの数値処理能力を要求しない、比較的高性能なアプリケーションの移行用に、新たな選択肢を提供します。

### 1.1 コアの特長

#### 1.1.1 16 ビット アーキテクチャ

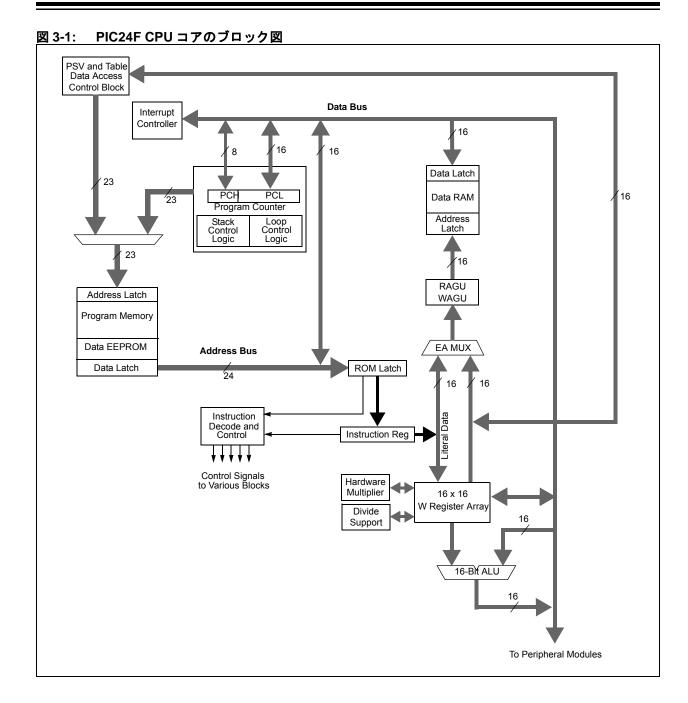

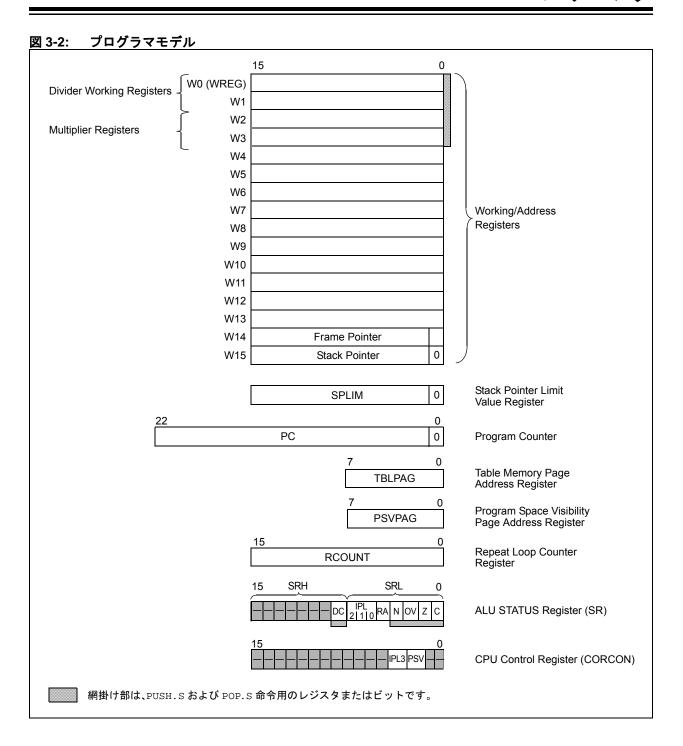

全てのPIC24Fデバイスの中核を成すのが16ビット改良型ハーバードアーキテクチャです。これはマイクロチップ社の dsPIC® デジタルシグナル コントローラに初めて採用されたアーキテクチャです。PIC24F CPUコアは、下記のように各種の性能 / 機能を備えます。

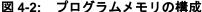

- 16 ビット データパスと 24 ビット アドレスパス: データメモリ空間とプログラムメモリ空間の間で データの移動が可能

- 単一の連続したアドレッシング: 最大 12M バイトのプログラム空間と 64K バイトの データ空間

- 16 個のワーキング レジスタで構成されたワーキング レジスタアレイ:ビルトイン ソフトウェア スタックをサポート

- 17 ビット x17 ビット ハードウェア乗算器: 整数計算をサポート

- ・ 32 ビット/16 ビット除算のハードウェア サポート

- 複数のアドレッシング モードをサポートし、高級言語 (C 等) 用に最適化された命令セット

- 最大 16 MIPS の動作性能

### 1.1.2 省電カテクノロジ

PIC24FV32KA304 ファミリの全デバイスは、動作時の 消費電力を大幅に低減する下記の機能を備えます。

#### ・ 動作中クロック切り換え:

動作中に、ソフトウェア制御でデバイスクロックを Timer1 または内部低消費電力RCオシレータに切り 換える事ができます。これを利用して、ソフトウェ アにユーザ独自の省電力機能を組み込む事ができま す。

#### ・ Doze モード動作:

シリアル通信等のタイミングが重要なアプリケーションにおいて、周辺モジュールを中断なく動作させる必要がある場合、CPU クロック速度だけを選択的に低減する事により、周辺モジュール用クロックを維持しながら消費電力を低減できます。

### ・ 命令ベースの省電力モード:

命令により下記の3種類の省電力モードを利用できます。

- アイドルモード:周辺モジュールを動作させたま まコアをシャットダウンします。

- スリープモード:コアと、システムクロックを必要とする周辺モジュールをシャットダウンします。独自のクロックまたは外部デバイスからのクロックを使用する周辺モジュールは動作を維持します。

- ディープスリープ モード: コア、周辺モジュール (RTCC と DSWDT を除く)、フラッシュ、SRAM をシャットダウンします。

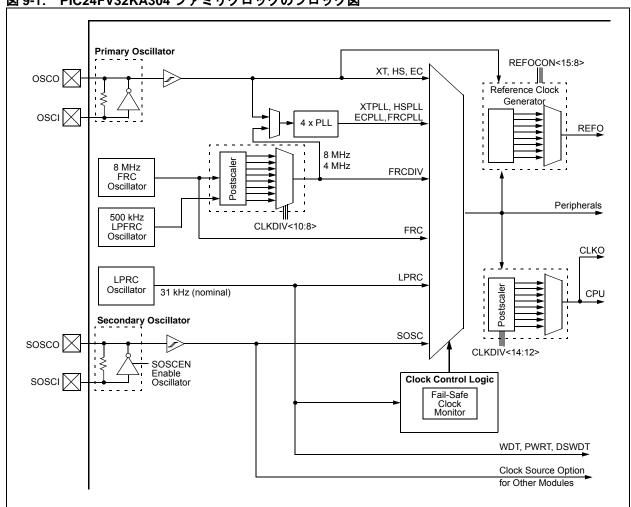

### 1.1.3 オシレータ オプションと機能

PIC24FV32KA304 ファミリは 5 種類のオシレータ オプションを備え、アプリケーション ハードウェアの開発に幅広い選択肢を提供します。これには下記が含まれます。

- 水晶またはセラミック振動子用の2種類の水晶振動 子モード

- 2 分周クロック出力オプションを備えた 2 種類の外 部クロックモード

- 2種類の高速内部オシレータ (FRC): 1 つは公称 8 MHz を出力し、もう 1 つは公称 500 kHz を出力します。これらの出力をソフトウェア制御で分周する事により、それぞれ 31 kHz または 2 kHz までクロック周波数を低減できます。

- 位相ロックループ (PLL) 周波数マルチプライヤを外部オシレータモードおよび 8 MHz FRC オシレータに併用する事により、クロック速度を最大 32 MHzまで増速できます。

- 処理速度を重視しないアプリケーション向けの低消 費電力オプションとして、出力が公称 31 kHz の内 部 RC オシレータ (LPRC) を使用できます。

内部オシレータ ブロックは、フェイルセーフ クロック監視機能 (FSCM) にも安定した参照ソースを供給します。FSCM は、メインクロック源を内部オシレータからの参照信号と対比する事によってクロックを常時監視します。メインクロック源に障害が生じた場合、コントローラはクロック源を内部オシレータに切り換えて低速動作を継続するか、あるいは安全にアプリケーションをシャットダウンできます。

#### 1.1.4 容易なデバイス移行

メモリサイズに関係なく、全てのデバイスが共通の充実した周辺モジュール機能セットを実装するため、アプリケーションの高性能化 / 高機能化に合わせてスムースな移行が可能です。

ピン配置もファミリ全体で一貫しているため、同一ピン数デバイス間だけでなく、例えば 20/28 ピンデバイスから 44/48 ピンデバイスへも容易に移行できます。

PIC24FファミリはdsPIC33ファミリとピン互換です。 さらに、PIC18 および dsPIC30 とも一部互換性を持ち ます。このため、比較的単純なものから高性能で複雑 なものまで、アプリケーションの能力を幅広く拡張で きます。

### 1.2 その他の特殊機能

### ・ 通信:

PIC24FV32KA304 ファミリは、幅広いアプリケーションの要求に応えるために、各種のシリアル通信周辺モジュールを実装しています。これには、マスタモードとスレーブモードの両方をサポートする $I^2C^{TM}$  モジュール、 $I^2DA^{BM}$  エンコーダ / デコーダを内蔵した UART モジュール、SPI モジュールが含まれます。

- リアル タイム クロック/カレンダ:

このモジュールは、機能を完備したアラーム付きのクロック/カレンダをハードウェアで実装し、コアアプリケーション用のタイマ リソースとプログラムメモリ空間を消費しません。

- 12 ビット A/D コンバータ:

プログラマブルなアクイジション時間を備えたこのモジュールは、サンプリング周期を待たずにチャンネルを選択して変換を開始でき、より高速な計測が可能です。16 段の結果バッファを使用する事により、スリープ時の消費電力を低減するか、あるいは動作モード時のスループットを改善できます。

- 充電時間計測ユニット (CTMU) インターフェイス: PIC24FV32KA304 ファミリは、静電容量式タッチセンシングおよび近接センシングと、精密な時間計測およびパルス生成に使用できる新しい CTMU インターフェイス モジュールを備えます。

### 1.3 ファミリ各製品の詳細

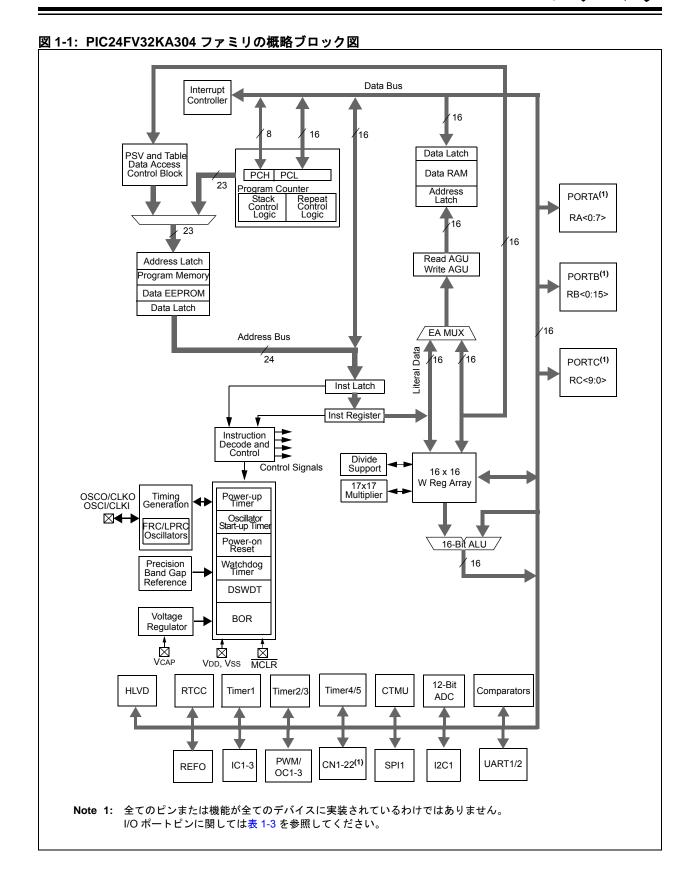

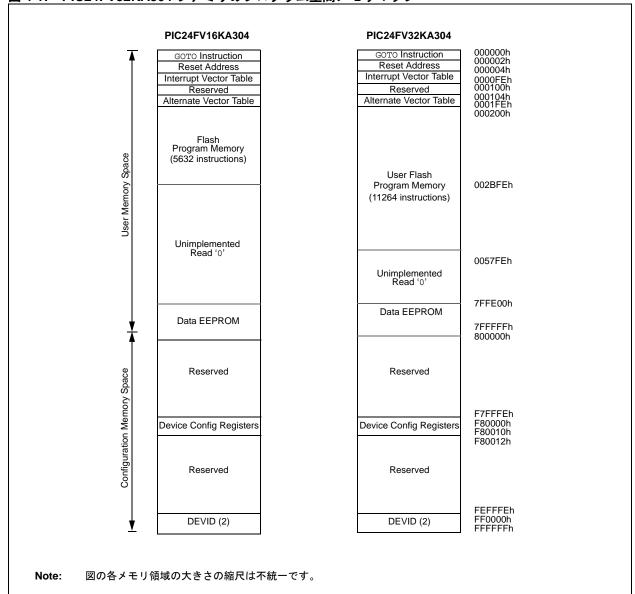

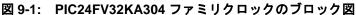

PIC24FV32KA304 ファミリは、20/28/44/48 ピンパッケージのデバイスを提供します。図 1-1 に、全デバイスに共通の概略ブロック図を示します。

デバイスによって下記の4項目が異なります。

- フラッシュ プログラムメモリ: PIC24FV16KA は 16K バイト、PIC24FV32KA は 32K バイトを実装

- I/O ピンとポートの数:

20 ピンデバイスでは 18 ピン /2 ポート、28 ピンデバイスでは 22 ピン /2 ポート、44/48 ピンデバイスでは 38 ピン/3 ポート

- 代替 SCL および SDA ピン:

20 ピンデバイスを除く 28/44/48 ピンデバイスの みで利用可能

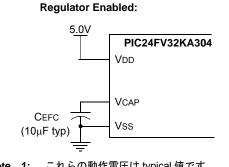

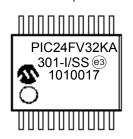

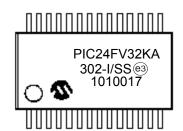

- 4. PIC24FV32KA301 ファミリには、標準デバイスと高耐圧デバイスが存在します。高耐圧デバイスの製品番号には「FV」が付きます(例:PIC24FV32KA304)。これらのデバイスはコア電源用の電圧レギュレータを内蔵し、2.0~5.5 Vの VDD レンジに対応します。周辺モジュールは VDD で動作します。標準デバイスの製品番号には「F」が付きます(例:PIC24F32KA304)。これらのデバイスは1.8~3.6 Vの VDD レンジで動作します。標準デバイスは電圧レギュレータを内蔵しないため、コアと周辺モジュールは直接 VDD からの電圧で動作します。

その他の全ての機能は本ファミリ内のデバイスで共通です。それらを表 1-1 に要約します。

PIC24FV32KA304ファミリデバイスで利用可能なピン機能を名称のアルファベット順に並べた一覧を表 1-3 に記載します。

Note:

表 1-3 は、個々の周辺機能に割り当てられているピン番号を示しますが、同一ピンに多重化されている他の機能については、p.5、p.6、p.7、p.8、p.9 のピン配置図を参照してください。これらの図には、多重化された複数の機能を優先度順に左から列挙しています(左端が最優先機能)。

### 表 1-1: PIC24FV32KA304 ファミリのデバイス機能

| 表 1-1: PIC24FV32KA304 フラ                 | アミリのナハイ                                                                                     | へ (成形          | 1                  |                | ı                                            | 1              |  |  |  |  |  |

|------------------------------------------|---------------------------------------------------------------------------------------------|----------------|--------------------|----------------|----------------------------------------------|----------------|--|--|--|--|--|

| 機能                                       | PIC24FV16KA301                                                                              | PIC24FV32KA301 | PIC24FV16KA302     | PIC24FV32KA302 | PIC24FV16KA304                               | PIC24FV32KA304 |  |  |  |  |  |

| 動作周波数                                    |                                                                                             |                | DC ~ 32            | MHz            |                                              |                |  |  |  |  |  |

| プログラムメモリ (byte)                          | 16K                                                                                         | 32K            | 16K                | 32K            | 16K                                          | 32K            |  |  |  |  |  |

| プログラムメモリ (命令数)                           | 5632                                                                                        | 11264          | 5632               | 11264          | 5632                                         | 11264          |  |  |  |  |  |

| データメモリ (byte)                            |                                                                                             |                | 2048               |                |                                              |                |  |  |  |  |  |

| データ EEPROM (byte)                        |                                                                                             |                | 512                |                |                                              |                |  |  |  |  |  |

| 割り込み要因<br>(ソフトベクタ/NMIトラップ)               |                                                                                             |                | 30 (26/            | 4)             |                                              |                |  |  |  |  |  |

| I/O ポート                                  | PORTA<br>PORTB<15:1                                                                         |                | PORTA<br>PORTB     | ,              | PORTA<11:7,5:0><br>PORTB<15:0><br>PORTC<9:0> |                |  |  |  |  |  |

| I/O ピンの総数                                | 17                                                                                          | 7              | 2:                 | 3              | 3                                            | 8              |  |  |  |  |  |

| タイマ:総数 (16 ビット)                          | 5                                                                                           |                |                    |                |                                              |                |  |  |  |  |  |

| 32 ビット<br>(16 ビットタイマのペアで構成)              |                                                                                             |                | 2                  |                |                                              |                |  |  |  |  |  |

| 入力キャプチャ チャンネル                            |                                                                                             |                | 3                  |                |                                              |                |  |  |  |  |  |

| 出力コンペア /PWM チャンネル                        |                                                                                             |                | 3                  |                |                                              |                |  |  |  |  |  |

| 入力状態変化通知割り込み                             | 16                                                                                          | 6              | 2:                 | 2              | 37                                           |                |  |  |  |  |  |

| シリアル通信 : UART<br>SPI (3 線 /4 線 )         | 2                                                                                           |                |                    |                |                                              |                |  |  |  |  |  |

| I <sup>2</sup> C™                        |                                                                                             |                | 2                  |                |                                              |                |  |  |  |  |  |

| 12 ビット アナログ / デジタル<br>モジュール ( 入力チャンネル数 ) | 12                                                                                          | 2              | 1:                 | 3              | 16                                           |                |  |  |  |  |  |

| アナログ コンパレータ                              |                                                                                             |                | 3                  |                |                                              |                |  |  |  |  |  |

| リセット (および遅延)                             | POR、BOR、RESET 命令、MCLR、WDT、不正オペコード、REPEAT 命令、ハードウェア トラップ、コンフィグレーション ワード不一致(PWRT、OST、PLL ロック) |                |                    |                |                                              |                |  |  |  |  |  |

| 命令セット                                    | 76 個                                                                                        | の基本命令、神        |                    |                | -ド オプショ                                      | ン              |  |  |  |  |  |

| パッケージ                                    | 20 E<br>PDIP/SSC                                                                            | <u>:</u> ン     | 28 t<br>SPDIP/SSOF | ピン             | 44 ピン QFN/TQFP<br>48 ピン UQFN                 |                |  |  |  |  |  |

表 1-2: PIC24F32KA304 ファミリのデバイス機能

| 衣 1-2: PIC24F32NA3U4 ファ                   |                                                                                            | * 134 11G     | 1                   |               | 1                                        | 1             |  |  |  |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------|---------------|---------------------|---------------|------------------------------------------|---------------|--|--|--|--|--|

| 機能                                        | PIC24F16KA301                                                                              | PIC24F32KA301 | PIC24F16KA302       | PIC24F32KA302 | PIC16F16KA304                            | PIC24F32KA304 |  |  |  |  |  |

| 動作周波数                                     |                                                                                            |               | DC ~ 32             | MHz           |                                          |               |  |  |  |  |  |

| プログラムメモリ (byte)                           | 16K                                                                                        | 32K           | 16K                 | 32K           | 16K                                      | 32K           |  |  |  |  |  |

| プログラムメモリ(命令数)                             | 5632                                                                                       | 11264         | 5632                | 11264         | 5632                                     | 11264         |  |  |  |  |  |

| データメモリ (byte)                             |                                                                                            |               | 2048                |               |                                          |               |  |  |  |  |  |

| データ EEPROM (byte)                         |                                                                                            |               | 512                 |               |                                          |               |  |  |  |  |  |

| 割り込み要因<br>(ソフトベクタ/NMIトラップ)                |                                                                                            |               | 30 (26/             | 4)            |                                          |               |  |  |  |  |  |

| I/O ポート                                   | PORTA<br>PORTB<15:12                                                                       |               | PORTA<br>PORTB      |               | PORTA<11:0><br>PORTB<15:0><br>PORTC<9:0> |               |  |  |  |  |  |

| I/O ピンの総数                                 | 18                                                                                         | 3             | 24                  | 4             | 3                                        | 9             |  |  |  |  |  |

| タイマ:総数 (16 ビット)                           | 5                                                                                          |               |                     |               |                                          |               |  |  |  |  |  |

| 32 ビット<br>(16 ビットタイマのペアで構成)               | 2                                                                                          |               |                     |               |                                          |               |  |  |  |  |  |

| 入力キャプチャ チャンネル                             | 3                                                                                          |               |                     |               |                                          |               |  |  |  |  |  |

| 出力コンペア /PWM チャンネル                         |                                                                                            |               | 3                   |               |                                          |               |  |  |  |  |  |

| 入力状態変化通知割り込み                              | 17                                                                                         | 7             | 2:                  | 3             | 38                                       |               |  |  |  |  |  |

| シリアル通信 : UART<br>SPI (3 線 /4 線 )          |                                                                                            |               | 2                   |               |                                          |               |  |  |  |  |  |

| I <sup>2</sup> C™                         |                                                                                            |               | 2                   |               |                                          |               |  |  |  |  |  |

| 12 ビット アナログ / デジタル モ<br>ジュール ( 入力チャンネル数 ) | 12                                                                                         | 2             | 1:                  | 3             | 1                                        | 6             |  |  |  |  |  |

| アナログ コンパレータ                               |                                                                                            |               | 3                   |               |                                          |               |  |  |  |  |  |

| リセット (および遅延)                              | POR、BOR、RESET 命令、MCLR、WDT、不正オペコード、REPEAT 命令、ハードウェア トラップ、コンフィグレーション ワード不-(PWRT、OST、PLL ロック) |               |                     |               |                                          |               |  |  |  |  |  |

| 命令セット                                     | 76 個 (                                                                                     | の基本命令、袖       | 复数のアドレ <sup>・</sup> | ッシング モー       | -ドオプショ                                   | ン             |  |  |  |  |  |

| パッケージ                                     | 20 E<br>PDIP/SSC                                                                           |               | 28 t<br>SPDIP/SSOF  |               | 44 ピン QFN/TQFP<br>48 ピン UQFN             |               |  |  |  |  |  |

### 表 1-3: PIC24FV32KA304 ファミリのピン配置

| <u> </u> | 10241 \$321                 |              | F                            |              | - <del></del>     |               |                             |              | F                                | V            |                   |               |     |                   |                                   |

|----------|-----------------------------|--------------|------------------------------|--------------|-------------------|---------------|-----------------------------|--------------|----------------------------------|--------------|-------------------|---------------|-----|-------------------|-----------------------------------|

|          |                             |              | ピン番                          | 号            |                   |               |                             |              | ピン                               | 番号           |                   |               |     |                   |                                   |

| 機能       | 20 ピン<br>PDIP/SSOP/<br>SOIC | 20 ピン<br>QFN | 28 ピン<br>SPDIP/SSOP/<br>SOIC | 28 ピン<br>QFN | 44 ピン<br>QFN/TQFP | 48 ピン<br>UQFN | 20 ピン<br>PDIP/SSOP/<br>SOIC | 20 ピン<br>QFN | 28 ピン<br>SPDIP/S<br>SOP/<br>SOIC | 28 ピン<br>QFN | 44 ピン<br>QFN/TQFP | 48 ピン<br>UQFN | 1/0 | <b>バッ</b><br>ファ   | 内容                                |

| AN0      | 2                           | 19           | 2                            | 27           | 19                | 21            | 2                           | 19           | 2                                | 27           | 19                | 21            | Ι   | ANA               | A/D アナログ入力                        |

| AN1      | 3                           | 20           | 3                            | 28           | 20                | 22            | 3                           | 20           | 3                                | 28           | 20                | 22            | Ι   | ANA               |                                   |

| AN2      | 4                           | 1            | 4                            | 1            | 21                | 23            | 4                           | 1            | 4                                | 1            | 21                | 23            | Ι   | ANA               |                                   |

| AN3      | 5                           | 2            | 5                            | 2            | 22                | 24            | 5                           | 2            | 5                                | 2            | 22                | 24            | Ι   | ANA               |                                   |

| AN4      | 6                           | 3            | 6                            | 3            | 23                | 25            | 6                           | 3            | 6                                | 3            | 23                | 25            | Ι   | ANA               |                                   |

| AN5      | _                           | _            | 7                            | 4            | 24                | 26            | _                           | ı            | 7                                | 4            | 24                | 26            | Ι   | ANA               |                                   |

| AN6      | _                           | _            | _                            | _            | 25                | 27            | _                           | ı            | _                                | _            | 25                | 27            | Ι   | ANA               |                                   |

| AN7      | _                           | _            | _                            | _            | 26                | 28            | 1                           |              | _                                | _            | 26                | 28            | - 1 | ANA               |                                   |

| AN8      | _                           | _            | _                            | _            | 27                | 29            | 1                           |              | _                                | _            | 27                | 29            | - 1 | ANA               |                                   |

| AN9      | 18                          | 15           | 26                           | 23           | 15                | 16            | 18                          | 15           | 26                               | 23           | 15                | 16            | - 1 | ANA               |                                   |

| AN10     | 17                          | 14           | 25                           | 22           | 14                | 15            | 17                          | 14           | 25                               | 22           | 14                | 15            | - 1 | ANA               |                                   |

| AN11     | 16                          | 13           | 24                           | 21           | 11                | 12            | 16                          | 13           | 24                               | 21           | 11                | 12            | - 1 | ANA               |                                   |

| AN12     | 15                          | 12           | 23                           | 20           | 10                | 11            | 15                          | 12           | 23                               | 20           | 10                | 11            | ı   | ANA               |                                   |

| AN13     | 7                           | 4            | 9                            | 6            | 30                | 33            | 7                           | 4            | 9                                | 6            | 30                | 33            | ı   | ANA               |                                   |

| AN14     | 8                           | 5            | 10                           | 7            | 31                | 34            | 8                           | 5            | 10                               | 7            | 31                | 34            | ı   | ANA               |                                   |

| AN15     | 9                           | 6            | 11                           | 8            | 33                | 36            | 9                           | 6            | 11                               | 8            | 33                | 36            | ı   | ANA               |                                   |

| ASCL1    | _                           | _            | 15                           | 12           | 42                | 46            | _                           | _            | 15                               | 12           | 42                | 46            | I/O | I <sup>2</sup> C™ | 代替 I <sup>2</sup> C 1 クロック入力 / 出力 |

| ASDA1    | _                           | _            | 14                           | 11           | 41                | 45            | _                           | _            | 14                               | 11           | 41                | 45            | I/O | I <sup>2</sup> C  | 代替 I <sup>2</sup> C 1 デジタル入 / 出力  |

| AVDD     | 20                          | 17           | 28                           | 25           | 17                | 18            | 20                          | 17           | 28                               | 25           | 17                | 18            | ı   | ANA               | A/D 電源ピン                          |

| AVss     | 19                          | 16           | 27                           | 24           | 16                | 17            | 19                          | 16           | 27                               | 24           | 16                | 17            | ı   | ANA               |                                   |

| C1INA    | 8                           | 5            | 7                            | 4            | 24                | 26            | 8                           | 5            | 7                                | 4            | 24                | 26            | ı   | ANA               | コンパレータ1入力 A (+)                   |

| C1INB    | 7                           | 4            | 6                            | 3            | 23                | 25            | 7                           | 4            | 6                                | 3            | 23                | 25            | ı   | ANA               | コンパレータ1入力 B (-)                   |

| C1INC    | 5                           | 2            | 5                            | 2            | 22                | 24            | 5                           | 2            | 5                                | 2            | 22                | 24            | ı   | ANA               | コンパレータ1入力C(+)                     |

| C1IND    | 4                           | 1            | 4                            | 1            | 21                | 23            | 4                           | 1            | 4                                | 1            | 21                | 23            | ı   | ANA               | コンパレータ1入力 D (-)                   |

| C1OUT    | 17                          | 14           | 25                           | 22           | 14                | 15            | 17                          | 14           | 25                               | 22           | 14                | 15            | 0   | _                 | コンパレータ 1 出力                       |

| C2INA    | 5                           | 2            | 5                            | 2            | 22                | 24            | 5                           | 2            | 5                                | 2            | 22                | 24            | ı   | ANA               | コンパレータ 2 入力 A (+)                 |

| C2INB    | 4                           | 1            | 4                            | 1            | 21                | 23            | 4                           | 1            | 4                                | 1            | 21                | 23            | ı   | ANA               | コンパレータ 2 入力 B (-)                 |

| C2INC    | 8                           | 5            | 7                            | 4            | 24                | 26            | 8                           | 5            | 7                                | 4            | 24                | 26            | ı   | ANA               | コンパレータ 2 入力 C (+)                 |

| C2IND    | 7                           | 4            | 6                            | 3            | 23                | 25            | 7                           | 4            | 6                                | 3            | 23                | 25            | ı   | ANA               | コンパレータ 2 入力 D (-)                 |

| C2OUT    | 14                          | 11           | 20                           | 17           | 7                 | 7             | 11                          | 8            | 16                               | 13           | 43                | 47            | 0   |                   | コンパレータ2出力                         |

PIC24FV32KA304 ファ

| 2 1 0. 1 |                             |              | <i>y y y y y y y y y y</i>   | <u> </u>     | <u> </u>          |               |                             | F\           | /                                |              |                  |               |     |          |                   |

|----------|-----------------------------|--------------|------------------------------|--------------|-------------------|---------------|-----------------------------|--------------|----------------------------------|--------------|------------------|---------------|-----|----------|-------------------|

|          |                             |              | ピン番                          | 号            |                   |               |                             |              | ピン                               | 番号           |                  |               |     |          |                   |

| 機能       | 20 ピン<br>PDIP/SSOP/<br>SOIC | 20 ピン<br>QFN | 28 ピン<br>SPDIP/SSOP/<br>SOIC | 28 ピン<br>QFN | 44 ピン<br>QFN/TQFP | 48 ピン<br>UQFN | 20 ピン<br>PDIP/SSOP/<br>SOIC | 20 ピン<br>QFN | 28 ピン<br>SPDIP/S<br>SOP/<br>SOIC | 28 ピン<br>QFN | 44ピン<br>QFN/TQFP | 48 ピン<br>UQFN | I/O | バッ<br>ファ | 内容                |

| C3INA    | 18                          | 15           | 26                           | 23           | 15                | 16            | 18                          | 15           | 26                               | 23           | 15               | 16            | I   | ANA      | コンパレータ 3 入力 A (+) |

| C3INB    | 17                          | 14           | 25                           | 22           | 14                | 15            | 17                          | 14           | 25                               | 22           | 14               | 15            | - 1 | ANA      | コンパレータ 3 入力 B (-) |

| C3INC    | 2                           | 19           | 2                            | 27           | 19                | 21            | 2                           | 19           | 2                                | 27           | 19               | 21            | - 1 | ANA      | コンパレータ 3 入力 C (+) |

| C3IND    | 4                           | 1            | 4                            | 1            | 21                | 23            | 4                           | 1            | 4                                | 1            | 21               | 23            | - 1 | ANA      | コンパレータ 3 入力 D (-) |

| C3OUT    | 12                          | 9            | 17                           | 14           | 44                | 48            | 12                          | 9            | 17                               | 14           | 44               | 48            | 0   | _        | コンパレータ 3 出力       |

| CLK I    | 7                           | 4            | 9                            | 6            | 30                | 33            | 7                           | 4            | 9                                | 6            | 30               | 33            | - 1 | ANA      | メインクロック入力         |

| CLKO     | 8                           | 5            | 10                           | 7            | 31                | 34            | 8                           | 5            | 10                               | 7            | 31               | 34            | 0   | _        | システムクロック出力        |

| CN0      | 10                          | 7            | 12                           | 9            | 34                | 37            | 10                          | 7            | 12                               | 9            | 34               | 37            | ı   | ST       | チャージ割り込み入力        |

| CN1      | 9                           | 6            | 11                           | 8            | 33                | 36            | 9                           | 6            | 11                               | 8            | 33               | 36            | ı   | ST       |                   |

| CN2      | 2                           | 19           | 2                            | 27           | 19                | 21            | 2                           | 19           | 2                                | 27           | 19               | 21            | I   | ST       |                   |

| CN3      | 3                           | 20           | 3                            | 28           | 20                | 22            | 3                           | 20           | 3                                | 28           | 20               | 22            | I   | ST       |                   |

| CN4      | 4                           | 1            | 4                            | 1            | 21                | 23            | 4                           | 1            | 4                                | 1            | 21               | 23            | I   | ST       |                   |

| CN5      | 5                           | 2            | 5                            | 2            | 22                | 24            | 5                           | 2            | 5                                | 2            | 22               | 24            | I   | ST       |                   |

| CN6      | 6                           | 3            | 6                            | 3            | 23                | 25            | 6                           | 3            | 6                                | 3            | 23               | 25            | I   | ST       |                   |

| CN7      |                             | _            | 7                            | 4            | 24                | 26            |                             | l            | 7                                | 4            | 24               | 26            | I   | ST       |                   |

| CN8      | 14                          | 11           | 20                           | 17           | 7                 | 7             |                             | l            |                                  | 1            | _                |               | I   | ST       |                   |

| CN9      |                             |              | 19                           | 16           | 6                 | 6             |                             | l            | 19                               | 16           | 6                | 6             | I   | ST       |                   |

| CN10     |                             |              | _                            | _            | 27                | 29            |                             | l            |                                  | 1            | 27               | 29            | I   | ST       |                   |

| CN11     | 18                          | 15           | 26                           | 23           | 15                | 16            | 18                          | 15           | 26                               | 23           | 15               | 16            | I   | ST       |                   |

| CN12     | 17                          | 14           | 25                           | 22           | 14                | 15            | 17                          | 14           | 25                               | 22           | 14               | 15            | _   | ST       |                   |

| CN13     | 16                          | 13           | 24                           | 21           | 11                | 12            | 16                          | 13           | 24                               | 21           | 11               | 12            | ı   | ST       |                   |

| CN14     | 15                          | 12           | 23                           | 20           | 10                | 11            | 15                          | 12           | 23                               | 20           | 10               | 11            | _   | ST       |                   |

| CN15     | -                           | _            | 22                           | 19           | 9                 | 10            |                             | ı            | 22                               | 19           | 9                | 10            | I   | ST       |                   |

| CN16     | -                           | _            | 21                           | 18           | 8                 | 9             | _                           | ı            | 21                               | 18           | 8                | 9             | I   | ST       |                   |

| CN17     | -                           | _            | _                            | _            | 3                 | 3             | _                           | ı            | _                                |              | 3                | 3             | Ι   | ST       |                   |

表 1-3: PIC24FV32KA304 ファミリのピン配置 (続き)

|        |                             |              | F                            |              |                   |               |                             |              | F                                | ٧            |                   |               |     |          |                       |

|--------|-----------------------------|--------------|------------------------------|--------------|-------------------|---------------|-----------------------------|--------------|----------------------------------|--------------|-------------------|---------------|-----|----------|-----------------------|

|        |                             |              | ピン種                          | 号            |                   |               |                             | ピン番号         |                                  |              |                   |               |     |          |                       |

| 機能     | 20 ピン<br>PDIP/SSOP/<br>SOIC | 20 ピン<br>QFN | 28 ピン<br>SPDIP/SSOP/<br>SOIC | 28 ピン<br>QFN | 44 ピン<br>QFN/TQFP | 48 ピン<br>UQFN | 20 ピン<br>PDIP/SSOP/<br>SOIC | 20 ピン<br>QFN | 28 ピン<br>SPDIP/S<br>SOP/<br>SOIC | 28 ピン<br>QFN | 44 ピン<br>QFN/TQFP | 48 ピン<br>UQFN | I/O | バッ<br>ファ | 内容                    |

| CN18   | _                           | _            | _                            | _            | 2                 | 2             | _                           | _            | _                                | _            | 2                 | 2             | I   | ST       |                       |

| CN19   |                             |              | _                            | _            | 5                 | 5             | _                           | _            | _                                |              | 5                 | 5             | I   | ST       |                       |

| CN20   |                             | _            | _                            | _            | 4                 | 4             | _                           | _            |                                  |              | 4                 | 4             | I   | ST       |                       |

| CN21   | 13                          | 10           | 18                           | 15           | 1                 | 1             | 13                          | 10           | 18                               | 15           | 1                 | 1             | I   | ST       |                       |